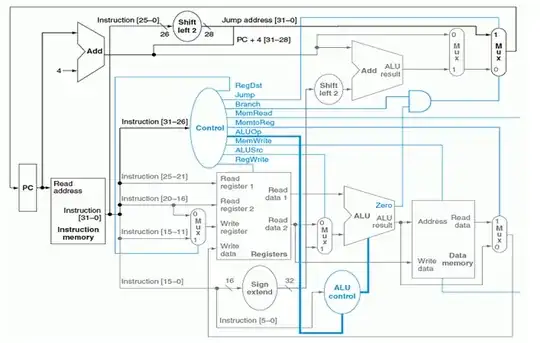

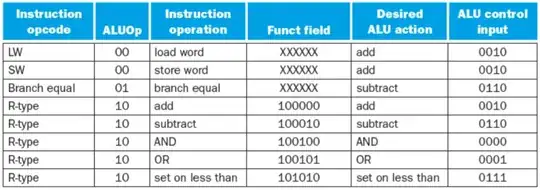

I am trying to include BNE instruction in the following circuit without introducing a new control line. I have thought of many possible ways like adding muxes or and gates etc to implement it but after implementation, a problem always occured with any of the three instructions, PC+4 , BEQ and sometimes BNE itself. Now I need a little advice from the experts on how can I implement bne without introducing a new control line.Here is the circuit: