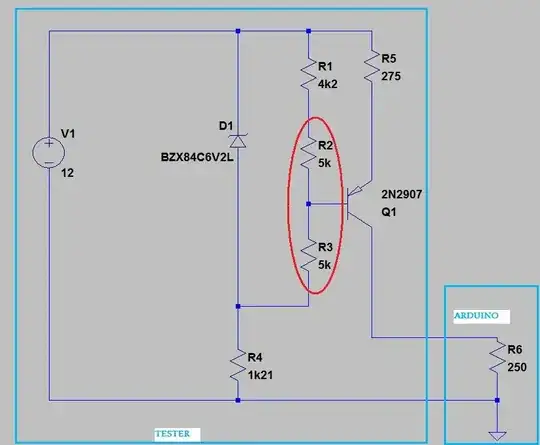

I am modeling a Push-Pull Converter in LTSpice and implemented this for a simple voltage feedback PWM control. This works great and I have added a bit on the end that allows for a maximum duty cycle control, as shown:

What I'm noticing is that when the duty cycle gets set to something low by the feedback control - under 10% - it starts to drive the two switches unequally during periods, e.g. one will be on for 40% and the other on for 7%. I tried putting another voltage source set to 10% pulses connected to each control line via a diode, but LTSpice did not like that.

Is there a better way to implement both maximum and minimum duty cycle control?

Alternatively, if someone can tell me why the switches are being driven unequally that would also be helpful.

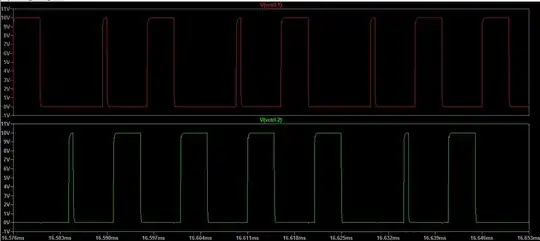

EDIT: I've included a screen grab of exactly what I'm talking about:

Sometimes the feedback will drive one switch for 40% and the other for ~7% in the same period and that is not acceptable. I am looking for a way to have the control say "this period the duty cycle will be 10%" for example, and force BOTH switch driving signals to be that duty cycle for the whole period. I have been trying something with the feedback signal as a reset for an SRFlop and "carving out" the off-time, but it's not working correctly.