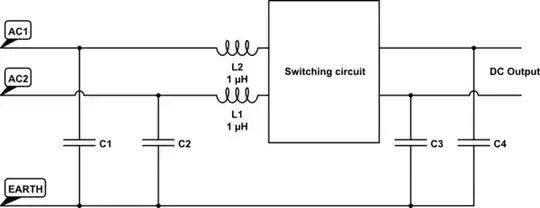

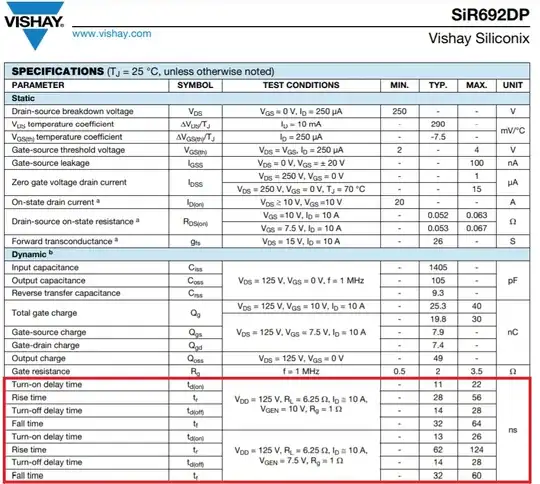

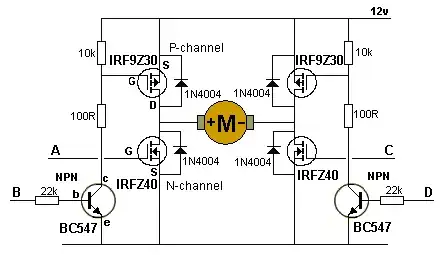

I'm working on a Flyback converter for approx. 28V/12V for 30W throughput. I'm using the IC "ADP1071-2" which provides isolation, and a lot of interesting features. I've been considering Vishay NMOSes for the switching transistor, and this being a flyback (discontinuous), most of low-Rdson MOSFETs have a higher Qg and thus heavy switch-off losses. Frequency of operation is 400 kHz.

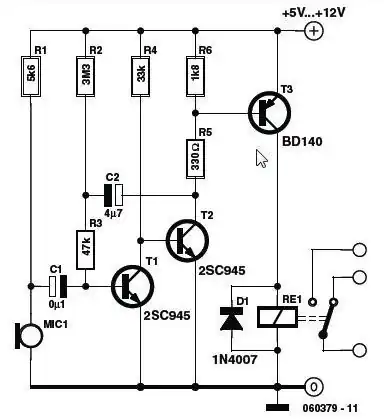

Is there (and there may not be any practical way to do this) a way to reduce fall-time of Q1 WITHOUT adding a driver IC and without disrupting the PWM IC ? I'm looking for something that would be 5 components max.

Down here is the switch-off profile : Blue is direct current, Red is Vds and green is dissipated power.