I just discovered something that I would like some expert to comment on.

CODE EXAMPLE A:

entity PipelinePoc is

Port ( clk : in STD_LOGIC;

led : out std_logic_vector(0 downto 0)

);

end PipelinePoc;

architecture Behavioral of PipelinePoc is

begin

process(clk) is

variable x : integer;

variable y : integer;

begin

if rising_edge(clk) then

if(x = 299)

then

x := 0;

if(y >= 500)

then

y := 0;

else

y := y + 1;

end if;

else

x := x + 1;

end if;

if((x+y) / 49 > 200)

then

led(0) <= '1';

else

led(0) <= '0';

end if;

end if;

end process;

end Behavioral;

CODE EXAMPLE B (Only difference is limited range on the integers):

entity PipelinePoc is

Port ( clk : in STD_LOGIC;

led : out std_logic_vector(0 downto 0)

);

end PipelinePoc;

architecture Behavioral of PipelinePoc is

begin

process(clk) is

variable x : integer range 0 to 1280 := 0;

variable y : integer range 0 to 960 := 0;

begin

if rising_edge(clk) then

if(x = 299)

then

x := 0;

if(y >= 500)

then

y := 0;

else

y := y + 1;

end if;

else

x := x + 1;

end if;

if((x+y) / 49 > 200)

then

led(0) <= '1';

else

led(0) <= '0';

end if;

end if;

end process;

end Behavioral;

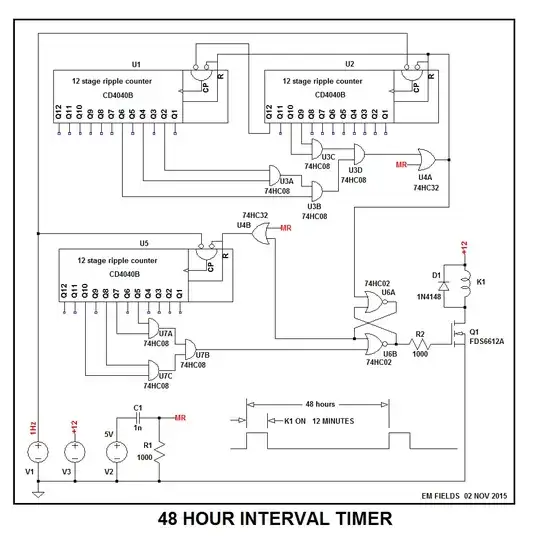

SCHEMATICS FOR EXAMPLE A:

SCHEMATICS FOR EXAMPLE B:

I would expect some difference between the example a with no range, assuming 32 bit may be representing the x and y values while the range 0 to 1280 can be represented with only 11 bit.

But the difference between the corresponding schematics is so huge, that either: - I may be missing some bug in my example be, allowing for the compiler to greatly simplify the logic - Or the FPGA has some small units that can do operations of a certain size (I am using a Basys3 board).

Can anyone explain why I end up with these very different schematics with only adding integer ranges?

Thanks