I have designed a buffer amplifier using an LM358 op-amp, with an input of a 1kHz sine wave and a power supply of +/-6V. whenever I increase the input sine amplitude above a certain threshold, I get a weird output (unlike the normal saturation that we all expect such as the one in Figure 1).

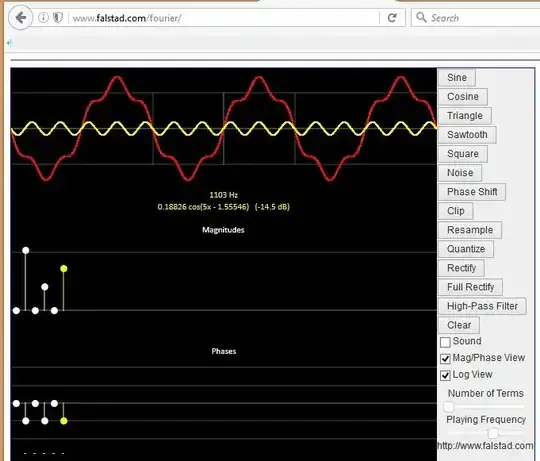

Figure 1 (Above). Normal saturation.

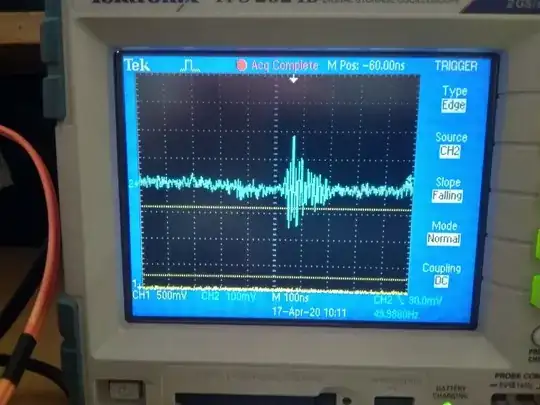

Figure 2 (Above). Weird unexpected saturation.

Why is the saturation in Figure 2 like that? I am used to Figure 1's output but not Figure 2. I guess it's linked to the -+ 6 Volt supply, but I'm really lost.

I've tried looking online for similar waveforms, but I found nothing.