I have a device that generates a 49.152MHz frequency, but depending on its status it can cut it off from time to time. This frequency synchronizes my MCU's audio devices, but it must never be stopped.

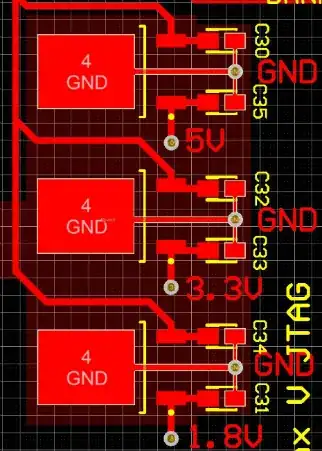

Is there a device like this:

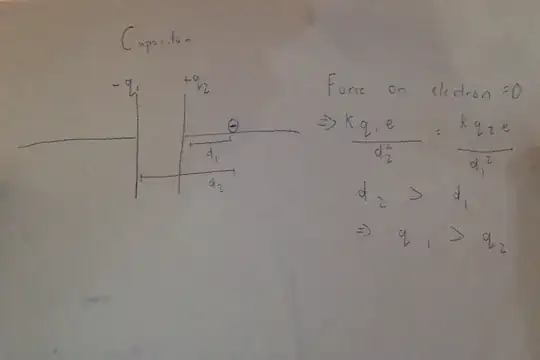

Or like this:

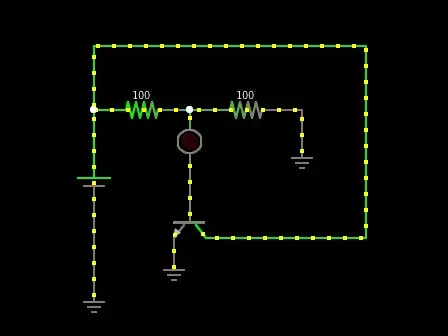

Or how can I design a circus to behave like this?

EDIT

Here is a (very simplified) outline of what I should do.

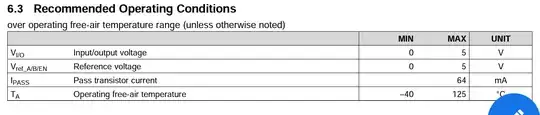

The backup clock generation could be a crystal or (to save money) could be a signal generated by the MCU itself.

If main clock is present the phase between out clock and main clock must be constant, and out clock should have no jitter (or no more than the main clock). When main clock goes off (or UXT is not populated) there should be a transition to backup clock. When main clock returns there should be a transition to it.

However jitter on clock out is not a problem compared to what the phase would be. I'm doing all this to synchronize everything with the clock recovered from the Dante stream. It may happen that the 48kHz recovered by Dante and the 48kHz obtained from my micro (and my crystal) have variable phase shift (e.g. one 48001 Hz and the other 47998). Wanting to avoid an ASRC the only solution is to make UXT master of all the clock domains. But we have to deal with the fact that UXT can shut down biefly the clock or it may not be populated (we have boards without Dante's capability), whereas ADC and DAC must always be clocked. Hence the need for a backup clock.

I have some area and cost constraints, so the solution should be not too big and definitely cheap.