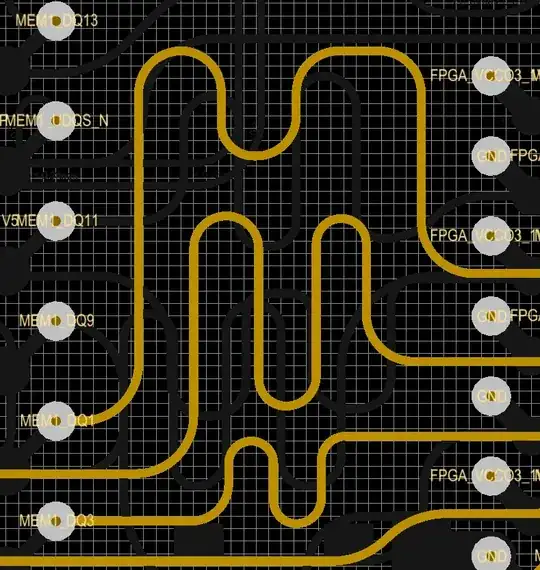

A colleague and I had a discussion and a disagreement about the different ways high speed signals can be length-matched. We were going with an example of a DDR3 layout.

All the signals in the picture below are DDR3 data signals, so they are very fast. To give you a sense of the scale, the entire X axis of the picture is 5.3mm and the Y axis is 5.8mm.

My argument was that, length matching done as in the middle trace in the picture can be detrimental to signal integrity, although this is just based on an intuition, I have no data to back this up. The traces in the top and bottom sides of the picture should have better signal quality, I thought, but again, I have no data to back this claim.

I would like to hear your opinions and especially experiences about this. Is there a rule of thumb for length matching high speed traces?

Unfortunately, I could not simulate this in our SI tool because it is having a difficulty in importing the IBIS model for the FPGA that we're using. If I can do that, I'll report back.