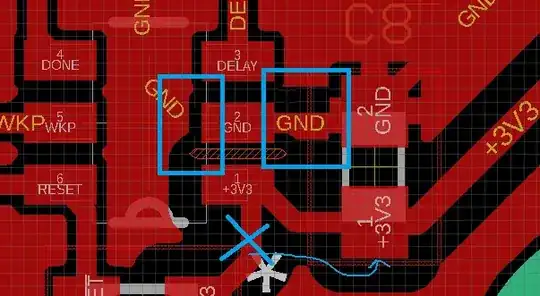

Your instructional diagram diagram is bogus for the most part (or at least, leaves certain rather important practical things unsaid). There's nothing wrong with A, B, C, or D (as long as D has a ground plane), at least until you get into the frequencies where everything is an antenna or transmission line. Adhering strictly to F and making concessions to do so can get you worse results until this point.

Going off of this guide, I understand that it is important that the current passes through VCC and GND directly through the capacitor.

No. Do not think of bypass capacitors as a warehouse where a truck carrying currents stop along the way to unload some of its cargo.

Think of bypass capacitors as operating on an AC high frequency circuit where the capacitor is the source superimposed on a DC circuit where the power supply is the source.

As long as you aren't at the point where everything is a transmission line or antenna, your objective is to minimize the distance/loop area/ inductance between the pin and the capacitor. That's all. Strictly making traces drop off at the cap before the pin at the expense of short traces and small loop areas just makes things worse until things like antenna stubs come into play.

For example, if a cap is under an IC, don't run traces from the plane to the cap then to the pin. Yes, it adheres to F but it also makes the trace length and loop area larger which makes things worse if you are not in the frequency range where antenna and transmission line effects matter. At those frequencies, everything you do matters including trace width, shape, the way corners bend, and PCB material characteristics.

From Electromagnetic Compatibility 2009 by Henry Ott: