I am designing a power supply to power two fiber-coupled diode arrays for a solid state laser. The diode arrays need a current controlled source of about 50 A and will have a voltage drop of < 2.2 V. The diode wavelengths drift with temperature so I need to be able to control the current output from diode tasing threshold (~12 A) up to the max of 50 A.

My prototype for this uses a MAX20096. This part at first look seems ideal: dual synchronous buck drivers with external MOSFET control and a SPI interface for control of driver current and status.

My design parameters are:

- VIn: 8 volts nominal (range 7.3-8.4 V)

- Vout: 2.2 volts

- Current set: 50 A

- Input ripple: 1%

- Output ripple: 1%

- Switching frequency: 500 kHz

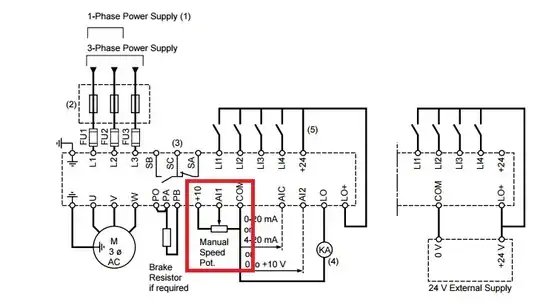

My schematic for this is below. My calculations were actually based on the MAX20078 data sheet - this is a single channel version of the same part and its data sheet was more comprehensive. The MAX20096 data sheet focuses mostly on the SPI interface. I built a prototype board so the crucial parts (mosfets, inductors) are on a circuit board and not a breadboard to minimize noise and allow me to take reasonable thermal measurements:

For a load, I have two high power diodes in series with a 100 mohm resistor. I have built a simple program on an Arduino to communicate with the MAX20096 and this seems to be working fine.

The MAX20096 allows me to set current as a % of maximum. I've set for about 2 A current to test and the results are not what I expect:

- The whole circuit rings like crazy. Noise shows up everywhere and is so bad it swamps the serial connection between the Arduino and my laptop so once I start it I can't reliably read status from the chip.

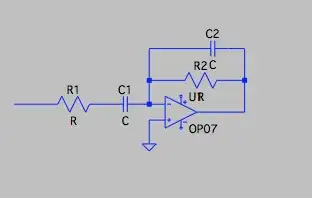

- The switching frequency is way off. I designed for 500 kHz but I'm measuring 100 kHz. And the frequency isn't stable enough to get the scope to lock into it (maybe confused due to the ringing?). I have measured the values of the R/C network forming the frequency selection and they are within tolerance.

- No matter what % of maximum current I choose I always read an output of 3.1 A from a connected ammeter and the duty cycle is the same. The 3.1 A varies if I change the load, so this isn't regulating at all.

- When I can read status from the SPI interface the current readings from the MAX20096 randomly go from 0-9 A. This is probably periodic but I'm not reading fast enough.

Here is an example of the ringing. The top yellow trace is the output, reading about 2 V. The bottom trace is the input to the inductor at about 8 V. Frequency here is about 96 kHz (the scope frequency readings are confused by the ringing):

A closeup of the ringing part of the waveform shows it's ringing at about 4.5 MHz:

Any idea what's causing this?

Also, I have some specific questions about the MAX20096 if anyone has experience with it:

- The chip uses independent oscillators for each channel and I'm concerned this could set up a beat frequency on the input supply that could require a bigger input filter. Would I be better off using a chip with a single oscillator that runs the channels out of phase? I am considering using the MAX17559ACJ+ and re-configuring it for current regulation. This would require more parts to interface with a microcontroller.

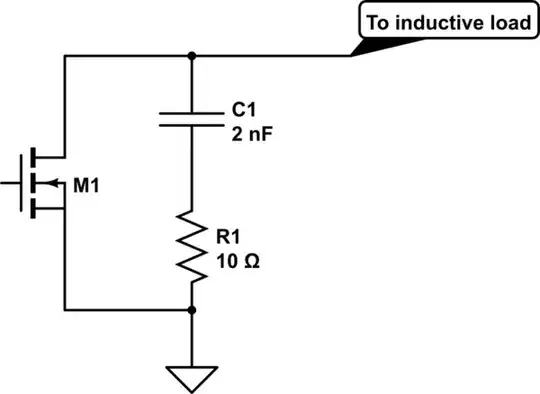

- These synchronous converters rely on the body diode for some conduction in the lower MOSFET to prevent shoot through. At high currents, would I be better off using a large external diode in addition to the MOSFET?

- Why is the switching frequency so far off?

- Why is the current read-back from the SPI interface so far off? (I'm wondering if the excessive ringing is causing noise back to the current sense inputs. I'm not using a kelvin connection to the current sense resistors and could be picking up junk here).

- Voltage read-back from the SPI interface is also way off. I even read random values from channels when they are off. Might also be due to noise here.

Anyway, any ideas that could nudge me in the right direction would be greatly appreciated. This is my first buck converter, so I'm sure I made a whole bunch of newbie mistakes.