I am just curious to understanding the working of this - Buffer IC (Part Number - 74AHC1G126)

My questions :

I figured out that this IC does not act as a level translator which changes the voltages levels of the output based on the input. Why would I be needing this IC which only replicates the voltage at the output from the input? Is the answer something like high impedance and reduce the loading of the source?

Where do we need to use these type of ICs?

Why are there like 7 inverters in the fig. 3 logic diagram?

I have read this previous question at this site but still not able to get clarity

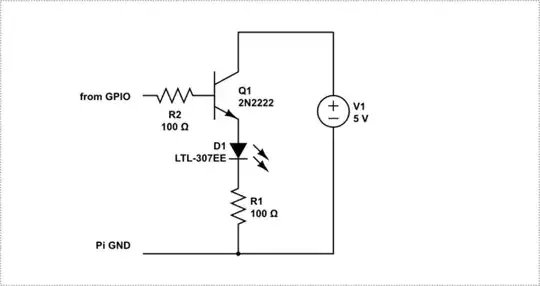

Please also help to understand the working of the circuit below (which is similar to my question) :