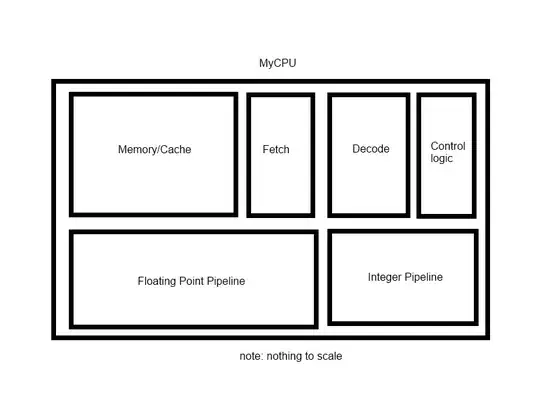

I was wondering if this is possible and if it is done in current designs. Seemed like an interesting enough idea to me. Here's a little diagram I made to help try and explain:

So let's say I'm clever and I build a bit of hardware that tracks the number of floating-point operations I've done lately. It tells me, hey, you haven't done any FP operations in the last 2000 instructions! And then decides to "power down" the whole floating point pipeline hardware. Of course, when a FP op does come up in the instruction queue, it needs to turn that power back on, maybe with a delay.

Does this make any sense? Can you "power down" specific parts of your chip and extract real power savings? How (physically speaking in terms of circuits) can you power down parts of hardware? And how hard is it to power them back up?

Sorry if this isn't a good traditional question! I know it's not very specific.

Cheers.