This question is similar to FET - Source follower utilizing current source to lower voltage offset, although I do not entirely understand the explanations, which is why I am posting my own question.

As part of an electronics lab, I was asked to build the following circuits.

I started with a simple follower:

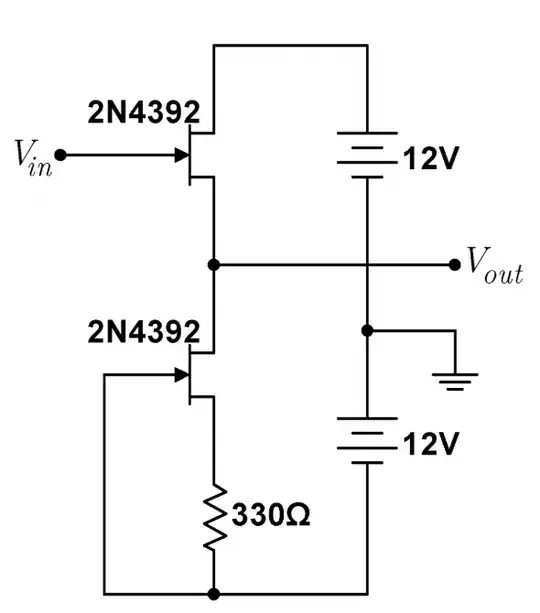

There was a constant offset from the +12V DC power supply, which makes sense. The goals were to remove this offset and increase the follower's gain. First, we were told to replace the source resistor with a current source:

And the gain increased substantially! I believe putting this current source in place of the resistor decreases signal attenuation that the JFET causes. I'm trying to understand why this is. Adding the current source stabilizes the current, and it makes sense that this could remove some signal attenuation, but how? Is it simply that the current source allows the circuit to more easily reach its equilibrium point?

This is only half the story. We also had to remove the offset. To do so, we added another source resistor to the upper leg of the circuit:

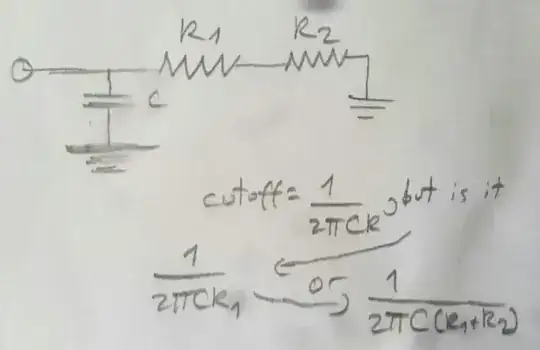

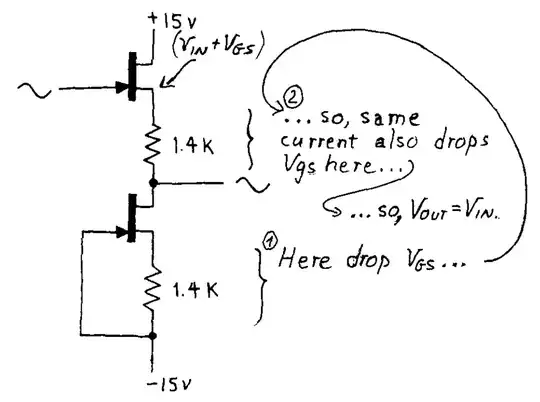

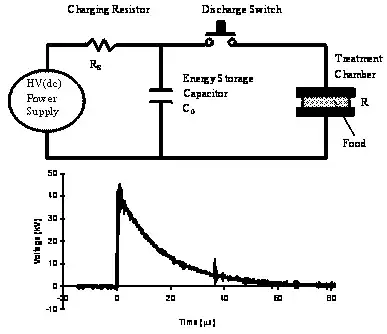

Now we have identical resistors above and below where we're measuring the output voltage. This is starting to look like a voltage divider. I was talking to one of the TAs in lab and he agreed that the voltage divider helps remove the +12V DC offset, although I'm not entirely sure why. Horowitz & Hill actually gives this exact scenario, and this is what they show:

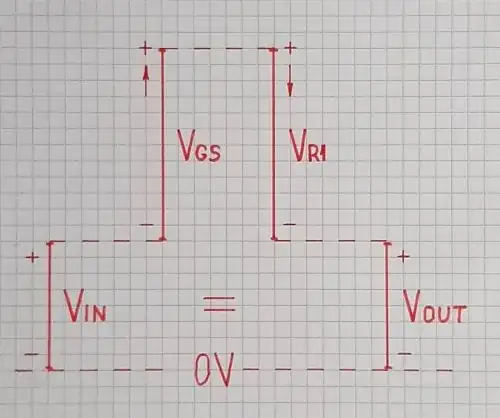

In the other post I linked above, the reasoning (as I understand it) was that as increases, a negative voltage grows across the JFET. How even much Vin increases is however much the negative voltage the JFET acquires. This causes the equivalent voltage drop across the upper resistor, so in will go down by the same value of that it went up. is also equivalent to the voltage drop across the bottom resistor. Mathematically, this is:

= − − =

I'm not entirely understanding this math and how it follows what I wrote out above. I know that to remove the offset, we want = , but I don't understand how what I wrote above actually amounts to this. So goes up by and we have + . Then it goes down by the same amount from the bottom resistor and then down by the same amount again from the bottom resistor. How does this effectively cancel out? Also, Horowitz & Hill says something similar: we start with + and drop by two . Again, how would this cancel to = ?

Thank you for helping me understand this.