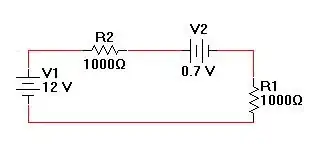

I am wondering what is the output resistance of the circuit below. I found that it depends on the gate voltage:

$$ \begin{aligned} R_{out} &= \frac{V_{out}}{I_{out}} \end{aligned} $$

$$ \begin{aligned} I_{out} &= I_{out_1} + I_{out_2} \\ &= \frac{V_{out}}{R_3} + I_{out_2} \end{aligned} $$

I convert the parallel current source in a series voltage source to find \$I_{out_2}\$:

$$ \begin{aligned} I_{out_2} &= \frac{V_{out} + g_m V_{gs} r_d}{r_d + R_4} \\ &= \frac{V_{out} + g_m(V_g - R_4 I_{out_2}) r_d}{r_d + R_4} \\ &= \frac{V_{out} + g_m V_g r_d}{rd + R_4 + g_m R_4 r_d} \\ &= \frac{V_{out} + g_m V_{in} r_d}{rd + R_4 + g_m R_4 r_d} \end{aligned} $$

I am wondering if my reasoning is correct. The problem sets solution is $$R_{out} = R_3 // (R_4 + r_d)$$ but I don’t understand how \$R_4\$ and \$r_d\$ can be in series because the current going through them doesn't seem to be the same according to the model.