Can someone explain this IC?

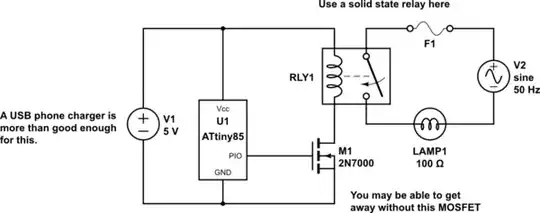

This "IC" is simply 2 separate N-channel MOSFETs bundled in the same package. This package is connected in a bidirectional level shifter fashion (however your circuit is incorrect, see below) used to translate low-speed signals from one voltage reference to the other. More info can be found on the WWW:

https://assets.nexperia.com/documents/application-note/AN10441.pdf

How does a bidirectional level shifter work?

Edit - Incorrect circuit! (refer to Michael Karas's answer to know why is that)

Why is this necessary? Why, for example, it would not be possible to use the 3V3 signals for i2c bus where the master runs at 5V?

It is rare in digital circuit design that you can mix and match different signal levels between ICs with different supplies levels. Most IC design input/output level range will be a function of their supply VCC:

- to interpret a "low" level, a very common formula is Vlow = 0.3 x VCC

- to interpret a "high" level, the formula becomes Vhigh = 0.7 x VCC

In your case, if you ran the 3.3V level I2C into the VCC = 5V IC, here is what the later will see:

- I2C low (about ground level ~ 0V) => IC reads "0" because Vin is under its "low" threshold which in this case is: 0.3 x VCC = 1.5V

- I2C high (~3.3V) => IC still reads "0" (not "1" as you'd expect) because Vin stays under its "high" threshold which in this case is: 0.7 x VCC = 3.5V

What are the dangers/problems associated with that?

From 3.3V to 5V, the problem is the one I described above, you'll misread the I2C bus instructions on the 5V IC.

From 5V to 3.3V, the main problem is activating the 3.3V IC input protection diodes which clamps the input to VCC + 0.7V. Therefore it will push current from the 5V rail through the pull-up resistor into the protection diode of the IC back into its 3.3V rail. You can calculate how much current is going through the diode will be approximately: Id = 1 / Rp (Rp = pull-up resistor value).

Using a 4.7kOhm pull-up, it gives you a current value of 0.2mA (200uA).

It may not sound much but you'll have to guarantee that your 3.3V IC can almost permanently clamp this level of current through its protection diode, otherwise, it may overheat and the input/output of the IC may become unusable.

And even if you believe you can make it work, for system reliability sake, don't :)

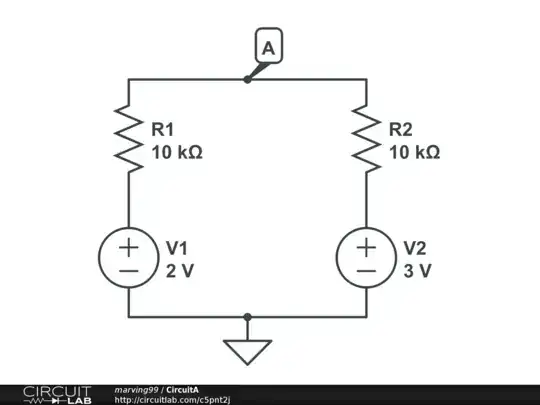

Now let's assume I will run both the master and the slaves at 3V3. Is this the correct way to pull the i2c lines up?

Yes, it is correct. You may not want to use "NMOSR" for the reference designator of the pull-up resistors (it is not necessary to name the reference designator based on the circuit it is used for, a simple "R" is enough, else you will get a very complex Bill of Materials) and use a unique I2C bus label name going to both ICs for simplicity and avoid confusion for both your schematic software and the reader.