This circuit solution is known as (BJT) differential pair, (BJT) differential amplifier, long-tailed pair, emitter-coupled pair... It has two inputs - the T1 and T2 bases. The input voltages are applied between the bases and ground; hence the name "single-ended voltages". The circuit amplifies only the difference between them (differential mode) but does not react to their average value (common mode). For example, when we want to measure the voltage across a "floating" element (that is not connected to ground), we are not interested in the voltages of its two terminals relative to ground but only of the voltage across it.

Structure. This behavior is achieved through an exotic circuit trick - by pairing two "common-emitter" amplifying stages. Their emitters are joined (hence the name emitter-coupled pair) and work on a common element with high resistance (hence the name long-tailed pair). So, to understand the meaning of this odd connection, you should understand very well the behavior of the single common-emitter amplifying stage.

> Common-emitter stage with fixed emitter voltage. In this configuration, we drive the transistor by applying the input voltage to the base. If the emitter voltage is fixed (the emitter is connected directly to ground or to a constant voltage source), the whole input voltage will be applied to the base-emitter junction (the transistor input) and we will achieve a maximum gain. So, the first conclusion is - fix the emitter voltage if you want a maximum gain.

> Common-emitter stage with "loose" emitter voltage. If we connect the emitter through a resistor to ground, then the emitter voltage will be not fixed but will change in the same direction as the input base voltage. This is because the transistor passes its output (collector) current through the resistor and "creates" a voltage drop across it that changes in the same direction as the input voltage. The problem is that we change the circuit input voltage at the base with the purpose to change the transistor input voltage across the base-emitter junction... but the transistor opposes our efforts by changing its emitter voltage in the same direction. This phenomenon is known as emitter degeneration and is a kind of negative feedback. The higher the resistance in the emitter, the stronger the effect ... and if we replace the resistor with the so-called "current source", it becomes maximum... the amplifying stage does not amplify. So, the second conclusion is - "loose" the emitter voltage if you want a minimum gain.

The general conclusion is: If you want to maximize the gain, fix the emitter voltage; if you want to minimize the gain, "release" it. This is what is done in the differential pair by pairing the two transistors.

Operation. The differential pair has different behavior depending on the operation mode:

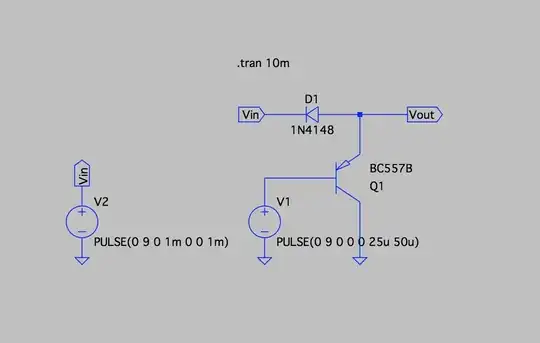

> Biasing (the OP's circuit represents this mode). First, an appropriate initial value of the emitter current must be set so that the transistors are in active mode and the output voltages are set in the middle of the operating range. This operation is known as biasing... and the OP's circuit diagram shows exactly this situation. Let's explore it in more detail because it is quite unusual here.

This procedure simply means to add another input voltage with constant value to the true input voltages that can vary during the circuit operation. The classic bias technique implies to apply the bias voltage/current in series or parallel to the input sources. Here it is made in a more clever way, from the side of the emitters by changing the value of the emitter current. We can see how on the OP's circuit diagram.

To control the transistors from the side of the emitter, the base voltages are fixed to zero by connecting the bases through 100 k resistors R1 and R5 to ground. The common emitter voltage has followed the input voltages with a small difference of about 0.7 V below.

The emitter current source exploits the inherent property of the transistor to keep its collector current constant when the input current/voltage is constant. So, it is just a transistor with a base resistor, i.e., a common-emitter stage with fixed (at -15 V) emitter voltage. The base resistor R6 sets the base and accordingly, the collector current that is actually the common emitter current of the differential pair.

Now the most interesting part of our explanation - adjusting the operating point. To adjust the bias current and accordingly, the operating point (as it is asked in the OP's question), we should vary the resistance of R6. This will make T3 change the emitter current of the pair. T1 and T2 will respond by adjusting their base-emitter voltages so that to pass the T3 collector current (negative feedback). As a result, T1 and T2 convey (each of them 1/2) the emitter current upwards to collector resistors R3 and R4. So, T1 and T2 can be thought as 1/2 bias current sources that create initial voltage drops across R3 and R4. As mentioned above, these drops should be set somewhere in the middle between ground (0 V) and the positive rail (+15 V). This procedure is known as adjusting the operating point.

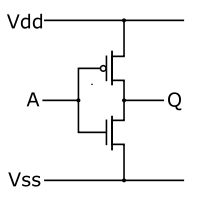

So you can think of your electronic circuit as of this electrical equivalent circuit:

> Amplifying. After the circuit is properly biased, we can apply the input voltages. In the OP's circuit, the input voltage sources are not shown. We can connect them in parallel to the base resistors R1 and R5 (directly or through capacitors) or insert them between the resistors and ground... or to remove the resistors at all... but it is important to ensure paths for the input bias currents. Why?

T1 and T2 not only adjust their base-emitter voltages according to the emitter current drawn by the current sink; this is accompanied by the flow of corresponding base currents (IC/beta). So, the negative feedback forces the transistors to sink these currents from the ground through the base resistors... and these currents should pass in some way. This is the role of the resistors - to ensure paths for the base currents if the input sources are not galvanic.

At differential mode, the input voltages change in opposite directions. The common emitter voltage is fixed in the middle between the input voltages since the transistors "pull" the common emitter point in opposite directions (like in tug of war or arm wrestling). The collector currents vigorously change (steer)... the output (collector) voltages vigorously change in opposite directions... and the gains are maximum.

At common mode, the input voltages change in the same direction. Both transistors act as one compound common-emitter stage with a current source in the emitter. So, the common emitter voltage follows the input voltages and the gains are minimum. The output (collector) currents and voltage drops across collector resistors do not change.

Finally, here are some specific recommendations for calculating the circuit. You can think of T1 and T2 as current sinks drawing 1/2 bias currents from the resistor network R2, R3 and R4 (see the picture above). The currents actually go to the negative power supply but here, for simplicity, I closed them to ground. R3 and R4 should be equal; then R2 will not influence the output voltages. I suppose that R4 is deliberately made different to show the error introduced by such an asymmetry.