I'm trying do design a mini-PCB, replacable half-bridge for motor control applications. The primary application is to use it with my modular inverter/BLDC/BDC controller. The controller design assumes 6 signals going to the bridge: GND, OUT, Low Side EN (optional), PWM, Gate Drive V (12V) and High Voltage (up to 60-70V DC), plus additional connectors for high-current HV and GND (up to several 10s of Amps).

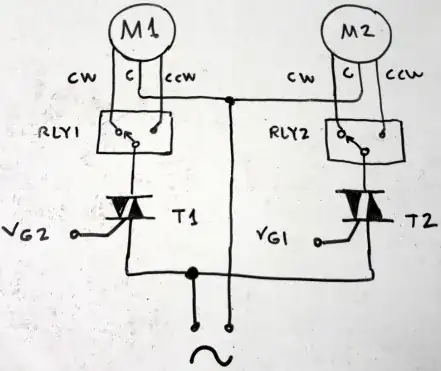

The initial design was made around MIC4102YM, thus the LSEN and only one PWM:

During tests with real hardware, either the MICs or the 5 ohm resistors kept blowing up, even with rather low "HV" of 12V. I thus replaced MIC4102YM with MIC4605-2YM (replaces LSEN with NC) and R1 with a 0.1A 10V linear regulator (78L10). Additionally, I've added another small capacitor between the regulator's GND and OUT legs. I also soldered only 2 out of 6 possible MOSFETs in case my problems were caused by too much gate charge. The MOSFETs are IPD60N10S4L-12.

This time, the tests with 12V input passed flawlessly. The PWM signal was at 10kHz with duty cycle between 0 and 99%. However, when tested with higher voltage (about 50V), "something" blew up and I must say I'm quite out of ideas as to why. The regulator and the resistors seem to be OK, but when testing with 12V again, I'm getting only ~0.5V gate voltage on the high side. The current drawn also seems to be higher than it should, as when PWM is pulled high, the voltage on the OUT leg drops to about 4-5V.

I'm currently ready to re-design the mini-board, but I'm not even sure what went wrong this time. Previously I could blame currents too high for the driver, but it doesn't seem to be the case this time (as it was working just fine with lower voltage on the driven side). Am I missing some crucial filters/safety features?

P.S. I'm open to suggestions regarding using other parts or more/less integrated solutions, as long as they can handle >100A peaks with 60V DC.

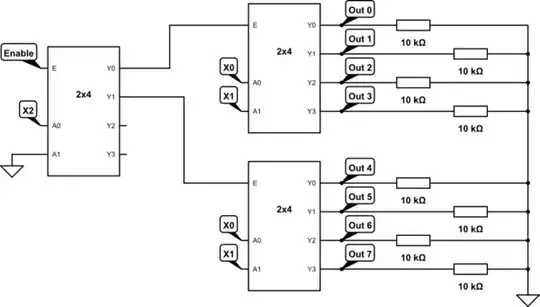

Edit: The original PCB layout (bottom layer, top layer contains 2-6 FETs only):