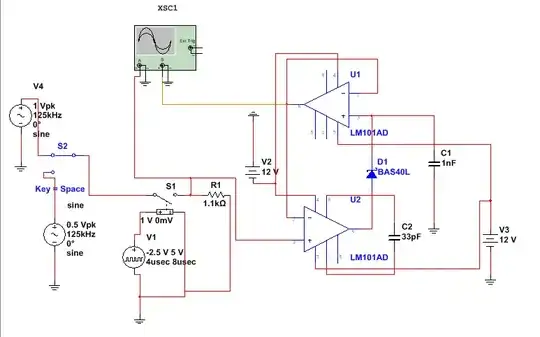

I have a problem with following oscillator circuit:

Assuming an ideal op-amp. I want to draw the output of Uout, Uc, U+.

First of all I want: \$Ua=f(U_+)\$

That is a simple voltage divider: \$U_+ = U_{out}\cdot\dfrac{R_1}{R_1+R_2}\$

After that I thought about what values can \$U_{out}\$ have and when?

\$U_{out} = 12V\$ when \$U_+ > U_-\$, \$U_{out} = -12V\$ when \$U_- > U_+\$

The capacitor will charge to \$U_{+}\$ because of an ideal opamp will hold \$U_D=U_+-U_-\$ to zero.

so with \$u_C(t=0)=0\$ I get:

\$u_C(t)=U_+(1-e^{-t/\tau})\$ with \$\tau = 9.1k\cdot100nF\$

So my question is first of all:

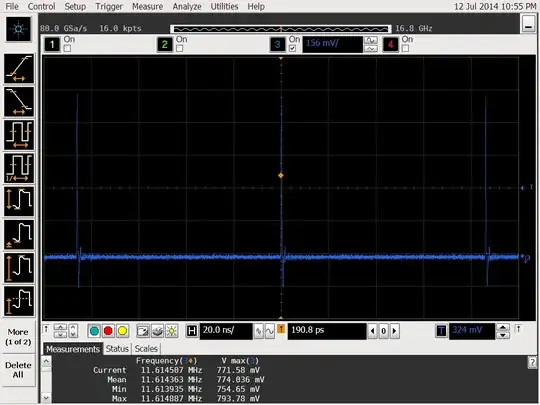

In case that NO energy is in my system, does it oscillate? -> Falstad shows an oscillation without any source connected (maybe noise?)

Since \$U_c\$ is decr/increasing to \$U_+\$, \$u_C\$ never reaches \$U_+\$, so WHY does the Comparator-Output Change? I thought that an Comparator works like this:

if \$U_+ > U_- -> U_{out}=Vcc_+\$

if \$U_- > U_+ -> U_{out}=Vcc_-\$

Maybe someone can help me to understand this? I have to learn a little bit more about oscillator circuits with opamps, so I have to learn the basic idea behind it. Hopefully someone can explain me that intuitively.

edit: I love it, maybe I got the answer myself after questioning.

\$Uc(t->\inf) = U_{out}\$ not \$Uc(t->\inf) = U_{+}\$

so there is an active case when \$U_- > U_+\$ so the Comp is switching.