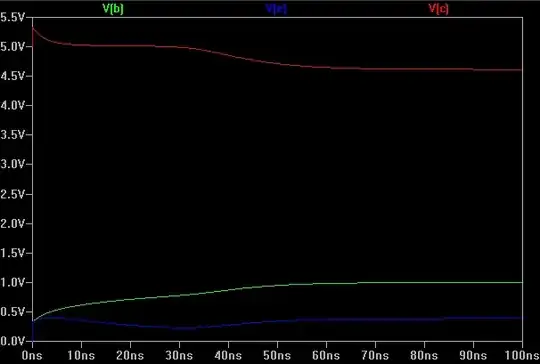

From the considerations above, we can conclude that, during the transition, the transistor can be thought as something slow... rather an integrator than an amplifier. So, to imagine how the transition is going, we can place ourselves in its place (empathy). The conceptual picture below can help understanding in this way. There I have visualized the voltages with vertical bars in red, which height is proportional to the voltage value (in association with a water column); the currents are represented by closed paths in green.

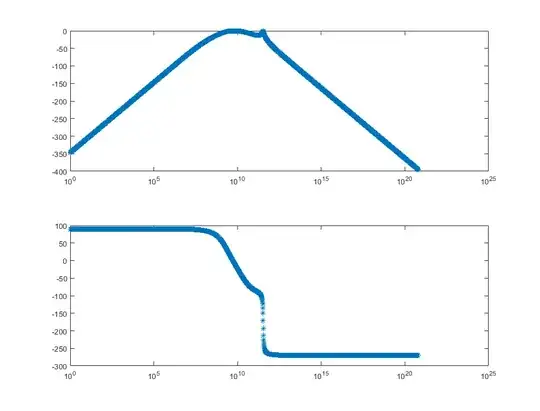

Here the output collector-emitter part of the transistor is emulated by a rheostat with variable resistance \$R_{CE}\$ so the stage is simply a triple voltage divider (\$R_{C1}\$, \$R_{CE}\$ and \$R_E\$) supplied by \$V_{CC}\$. The little man (we) is keeping \$V_E = V_{IN}\$ by moving the slider of the collector-emitter rheostat \$R_{CE}\$. For this purpose, he observes the base-emitter zero indicator and changes the rheostat resistance in the respective direction to zero the indicator reading. By the way, the "man-emulated transistor" precisely equalizes \$V_E\$ to \$V_{IN}\$ (there is no \$V_{BE}\$ here)... and there is no current (\$I_B\$) drawn from the input source (the indicator is bootstrapped).

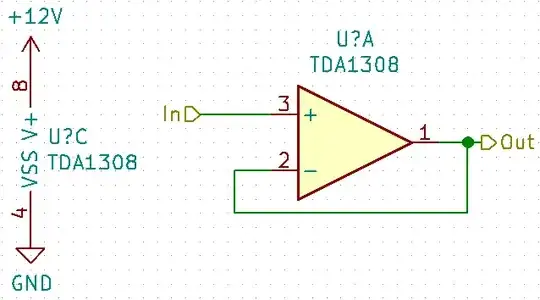

Since the current of this circuit of three resistors in series is the same, there is the same proportion between the voltages and resistances - the ubiquitous \$V_{RC}/V_E = R_C/R_E\$ and this is the gain of the stage. We can see a similar idea in the op-amp inverting and non-inverting amplifiers where the op-amp plays the role of \$R_{CE}\$ (or, more precisely, of "varying \$V_{CC}\$")... only it is not inserted between the other resistors but out of them.

Indeed, there is no base resistor in this picture but its role is minor in this configuration.