I need help understanding how to calculate tpd while static hazards are involved,

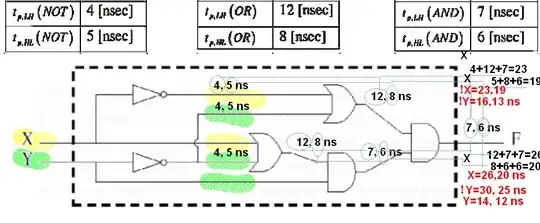

Given this circuit: (the output F is constant 0)

I found out that if X and Y are initated to 0 and we change Y to 1 we get an hazard after the AND gates (0->1->0) which I know cause a delay in the circuit even though the output is constant.

I found out that if X and Y are initated to 0 and we change Y to 1 we get an hazard after the AND gates (0->1->0) which I know cause a delay in the circuit even though the output is constant.

I am having trouble understanding how to calculate the delay, for example what delay should I take into consideration (HL,LH) for the AND gates.

If I could get an explaintion and an example calculating the delay from Y to F it would help a lot (not graphic if possible).