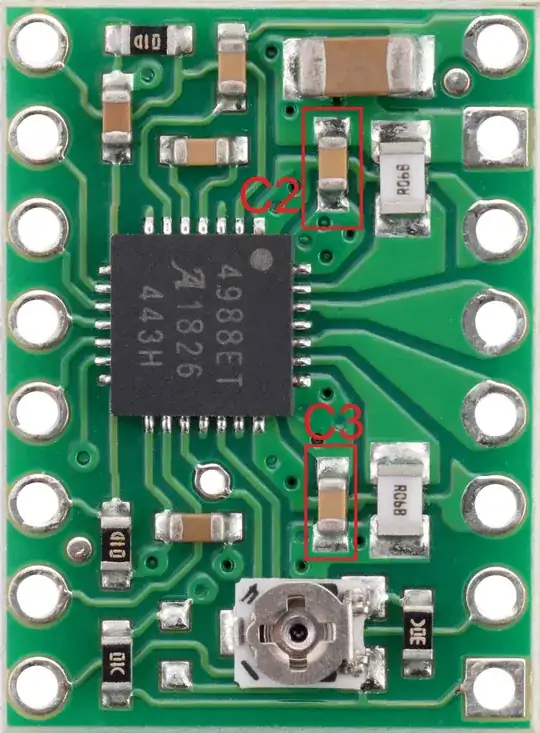

Below is the schematic of the Pololu A4988 driver board:

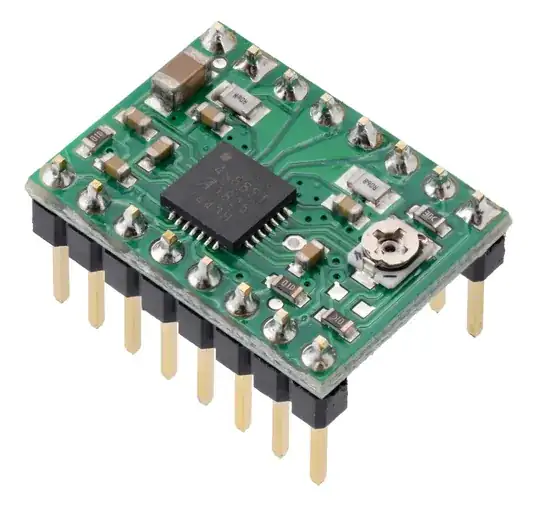

There are three capacitors on the motor power input. I can understand why engineers decided to use separate 4.7 µF with larger size (1206, 0.1 µF are either 0805 or 0402): because physically small capacitors have lower ESR, and they effectively filter out higher frequencies (correct me if I'm wrong). But what is the reason to use two 0.1 µF capacitors in parallel? Can they be replaced by a single 0.22 µF in order to save PCB space and cost?

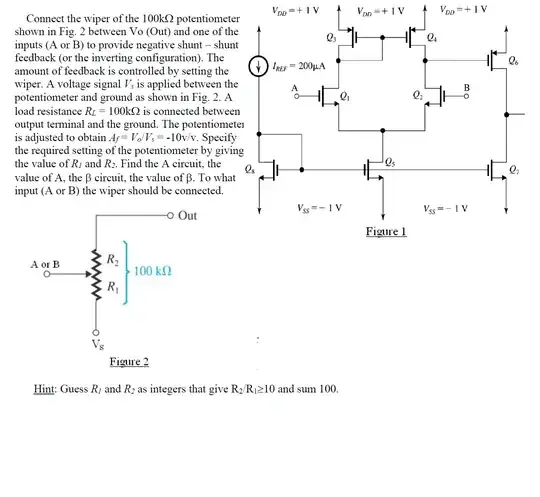

Image of the board; it can be clearly seen that all capacitors are ceramic: