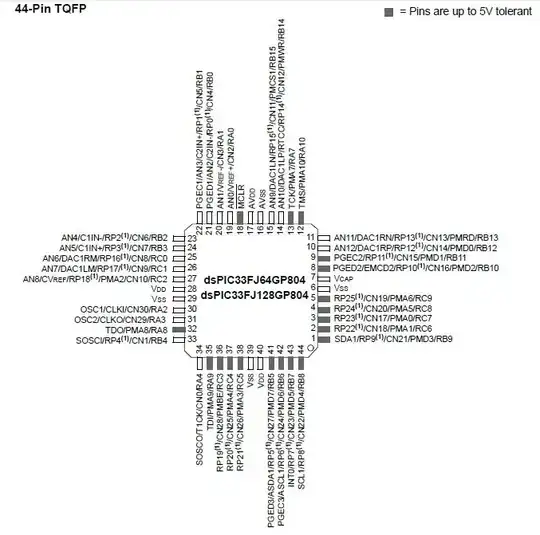

I'm trying to build a 16kHz single phase, full bridge PWM inverter, Vdc=380V, 2kVA rated.

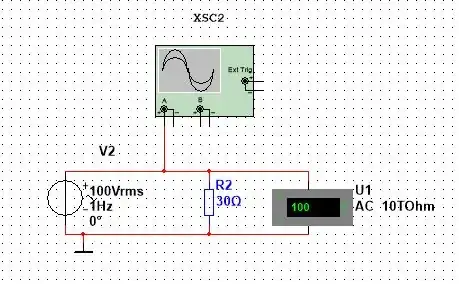

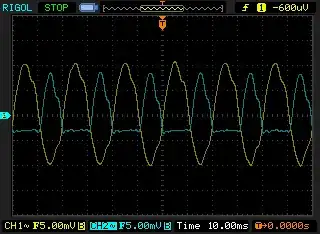

When I load the inverter a little bit, the output voltage waveform is looks like this:

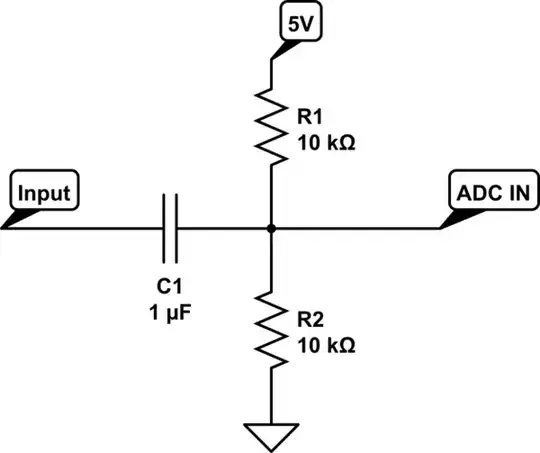

simulate this circuit – Schematic created using CircuitLab

I have capacitor snubbers across each half bridge as shown in the schematic.

How can I get rid of the distortion in the red circle?

Added:

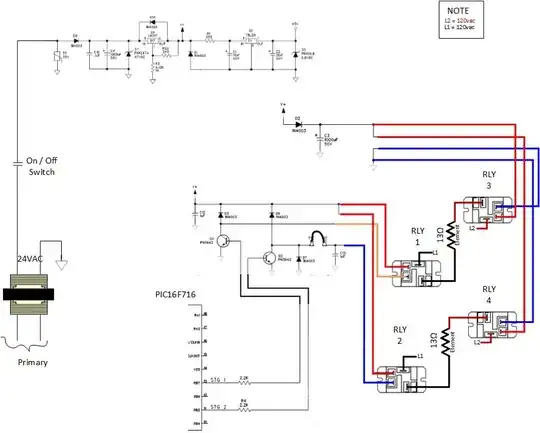

Here is one of four PWMs (I only have one probe so I can't show you all four same time, but I've checked phase differences and they're ok. Other PWMs have same duty cycle and Vpp like this.):

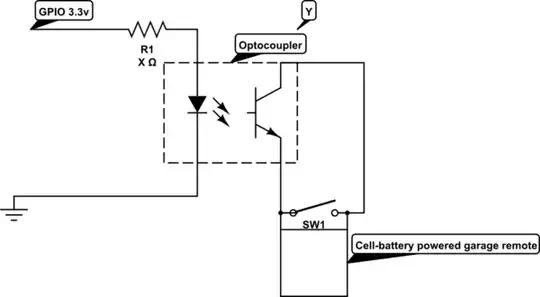

Here is the driving circuit (I have 2 of these for each half bridge.):

Here is the rising edge of one PWM, purple is pwm signal and blue is output of driver circuit.

Here is falling edge of same PWM above

Here is all four mosfet's Vgs waves

Here is all four PWM