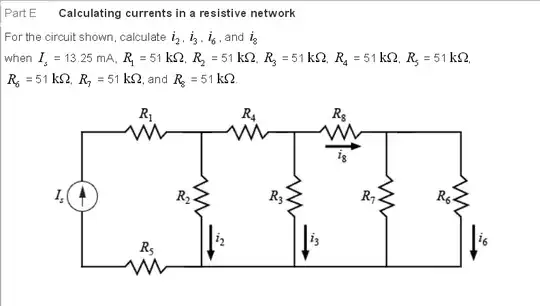

Two Problems

- Current only while switching.

You need a complementary design to solve this. Something to hold it high (that can be switched off, not a static resistor), and something to hold it low. And they need to be driven alternately.

So you will need two level shifters (like the NPN with emitter resistor), one which drives a pull-up switch (common emitter PNP). And they need to be driven inversely, whether from one inverted, or perhaps by making one common-emitter and the other common-base.

Another option is a differential pair, which has different limitations on voltage range (not a problem here, but might be important if the supply voltage is highly variable, say it should work from 5 to 80V?), but also offers a more precise/customizable input threshold (it can be used as a comparator).

- Excessive power dissipation.

The pull-down transistor has to sink full drive current divided by emitter follower hFE. So, easily a few mA for typical applications. That's easily some 100mW, which still isn't game-over for a SOT-23 for example, but one will definitely run hot, and it's not very scalable -- it's not going to work at 600V, or if you need 10A peak, say.

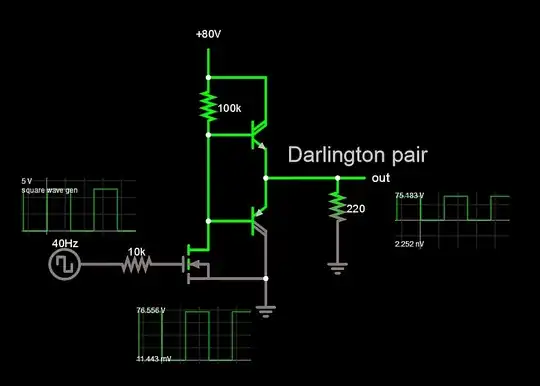

The pull-down emitter follower (PNP) meanwhile has to sink full load current from GND. That's already a huge liability at 80V, even with larger packages (say SOT-223 or DPAK); and it's just poor efficiency. This is easily solved by introducing a "bootstrap" rail, "hanging down" from the supply, i.e. a 12V supply with its positive tied with +80V.

Note that the zener diode can go away, or perhaps be moved to the supply instead, in this case: the complementary emitter follower can be driven at most VBE outside of its supply rails -- it's self-clamping. (Indeed, we might even use that clamped current to power the supply. Hmm...)

Examples

Some related examples can be found on my website:

https://www.seventransistorlabs.com/ClassD1/Images/ClassD_GD.png

The two NPNs bottom-left (dang, I should've put designators on these, alas) accept a logic-level input, while giving complementary open-collector outputs. (Both are designed to saturate; for current-mode outputs, both transistors need emitter resistors.)

The remainder of this circuit has interesting function, but isn't relevant here. I will only briefly explain: the PNP pull-ups are nominally constant-current sources, but notice when one is saturated, it pulls down (well, up) the base voltage, cutting off the other. In this complementary-output circuit, that saves bias current. (For a single output, this wouldn't be helpful.) The right side is just emitter followers, of course.

https://www.seventransistorlabs.com/Images/CMBuck_Output.png

This demonstrates a complementary gate drive circuit, with a logic-level input referenced to the negative supply (COMPOUT), differential pairs for generating the complementary currents (Q301/Q302, Q303/Q304), and actually one switch (Q311, the pull-up switch), and two cascaded (Q312 into Q313), for the output drive: this provides higher current output than using the current-mode signal directly, i.e. using Q301's current directly to tug on the gain node (ZXTC bases) would be quite weak and require excessive dissipation in it (well, or more specifically its cascode Q305; the cascodes are an optional feature here).

This also demonstrates complementary outputs for N-channel MOSFETs, if a half-bridge design is required.

The HS_12V supply is provided by a small DC-DC converter. For the P-channel case, this can be a 12V supply "hanging down" from the 80V supply.

As you can see, it's a lot more components, for not a lot of value.

Using standard solutions is best whenever possible. Unfortunately there are few (proper) P-channel drivers, nor (dedicated or paired) high-side N-channel drivers with built-in charge pump. (And making your own charge pump is annoying, and not practical anyway at higher voltages.)