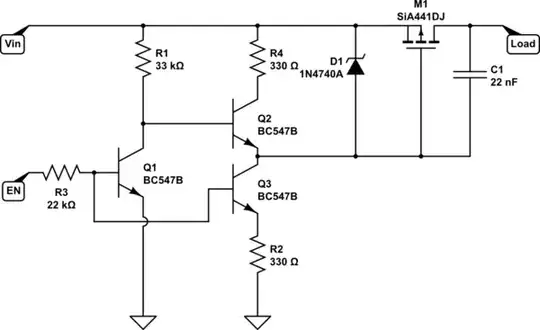

I am designing a simple current control circuit and trying to simulate it in LT Spice. The circuit is not optimized for some real-world application, it's more a learning method for me to get grip on stability analysis.

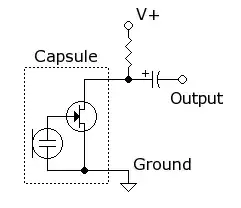

The circuit consists of a voltage controlled MOSFET M1 and a simple diff. amp U4 for voltage measurement. The measured voltage is compared to set voltage (VSET) and the comparator control the MOSFET gate.

For AC analysis I followed the instructions from this LT Spice video, and inserted an AC stimulus V4 at the high-impedance input of U2. I ran some simulation with varying capacitance for C1 and got this nice and stable Bode:

where my gain margin was 18dB and phase margin 132°. No resonance peaks, all nice and clear. According to the theory I'm familiar with, this should be nice and stable circuit. But the moment I remove the AC stimulus and insert the DC pulse at VSET, I get the step response like this:

Now, I'm quite confused. What sense does it make to have two opposite stability outputs? Aren't trasient and ac analysis compatible?