I'm trying to minimize the impedance from my capacitors to the Gnd and Power planes.

1. Via positioning

I've learned from several sources that the best via positioning is close to each other. This way you minimize the loop inductance for currents flowing between the capacitor and the Gnd/Power planes.

The best article I found on this topic is Via configurations for connecting decoupling capacitors from All About Circuits (see https://www.allaboutcircuits.com/technical-articles/different-via-configurations-for-connecting-decoupling-capacitors/). A figure from that page:

2. Via size

I don't know how to choose the ideal via size. I know that small vias have more resistance and higher self-inductance. This is what you can calculate with this online tool: http://referencedesigner.com/rfcal/cal_13.php

But smaller vias can be positioned closer to each other. The loop inductance is therefore much smaller.

Thank you @Huisman to point out that my big and small vias (see details in next paragraph) are in fact equally spaced if you measure their distance edge-to-edge: Both have 0.175 mm annular ring size and 0.125 mm clearance.

However, if you rely on the center-points for distance measurement, they are no longer equally spaced. So it depends on how you measure the "via distance".

So what is actually the ideal via size, to maximize the effect of the capacitor? Suppose that the ideal via size is rather big, I'd like to know how much extra impedance I cause by choosing for the small via anyway. In other words, is it worthwile to go for the bigger vias?

3. Some details

3.1 Via details

---------------------

Normal via

- Via diameter: 0.7 mm [27.56 mil]

- Finished hole diameter: 0.35 mm [13.78 mil]

- Annular ring: 0.175 mm [6.89 mil]

- Minimal clearance: 0.125 mm [4.92 mil]

Small via

- Via diameter: 0.5 mm [19.67 mil]

- Finished hole diameter: 0.15 mm [5.91 mil]

- Annular ring: 0.175 mm [6.89 mil]

- Minimal clearance: 0.125 mm [4.92 mil]

Please help me to choose which via is best to connect the capacitors to the Gnd/Power planes.

3.2 Capacitor details

------------------------------

I mostly use ceramic capacitors:

- 100nF Close to chip power pins, also connected to vias for Power/Gnd connection.

- 1uF Next to the 100nF ones.

- 10uF dispersed all around the board, connected to Power/Gnd planes.

3.3 Frequency region of interest

-----------------------------------------------

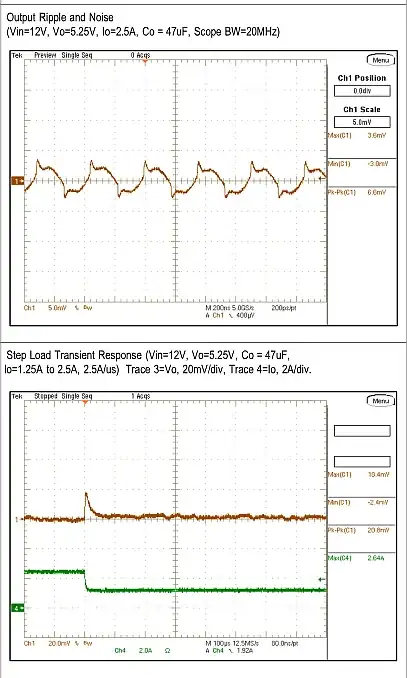

For my current project, I need to get a clean 5V from a step-down converter based on the AP1501-50K5G-13 chip (see https://www.diodes.com/assets/Datasheets/AP1501.pdf).

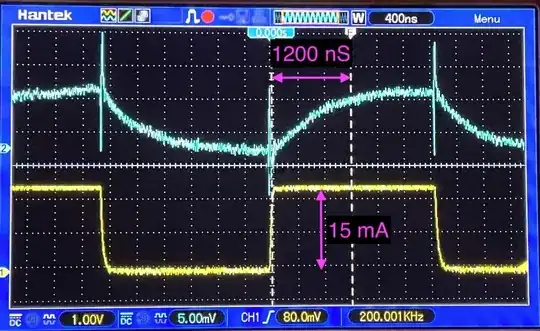

This DC-DC converter chip operates at approximately 150kHz. However, it generates noise in the MHz range as well, because of the sharp switching edges. Perhaps even in the GHz region - I don't know.

Aside from my current project, I'd like to know the ideal via choice for all kinds of frequencies.

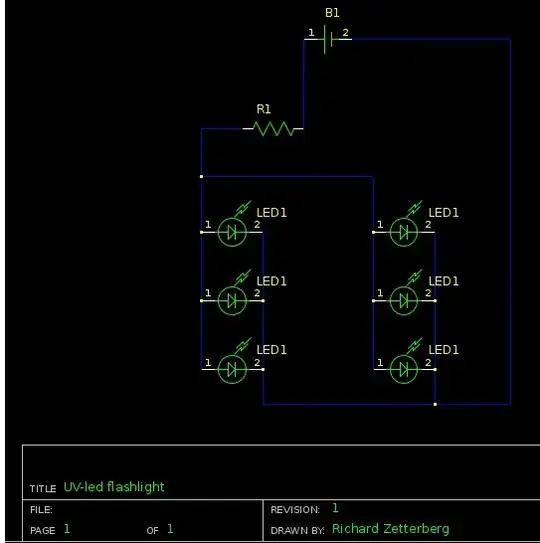

4. Quantify the impact [+50 bonus points]

I read interesting ideas and "rules of thumb" in the provided answers. But nobody calculated/simulated a specific example.

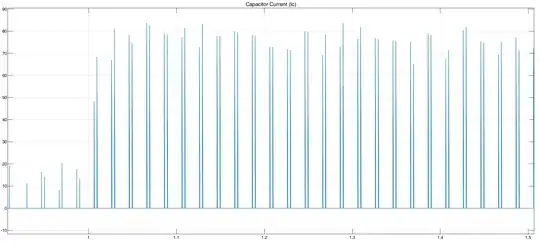

If you've got the right simulation software (I don't), perhaps you could do some simulations to get graphs like this:

I believe we could discover interesting trends from such simulations. I'd be very thankful :-)