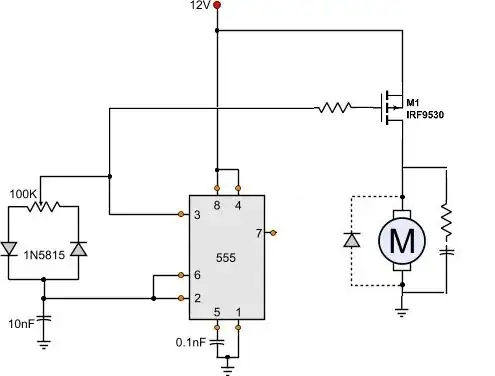

simulate this circuit – Schematic created using CircuitLab

This is a simplified example of a push pull GPIO found in most microprocessors, with a load attached.

Using the capacitance and current values from the datasheet that is usually given in a microprocessor datasheet, how can the rise time be calculated?