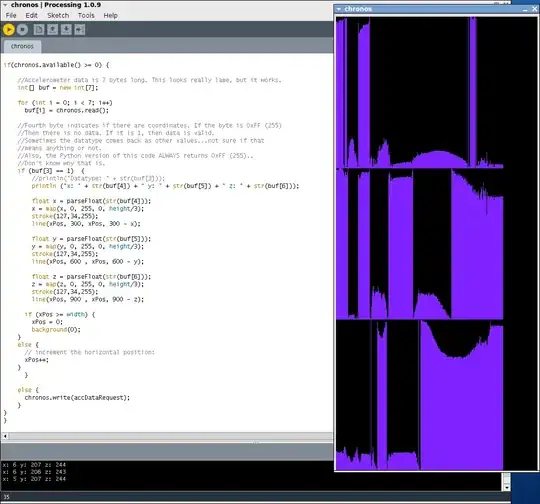

simulate this circuit – Schematic created using CircuitLab

I feel as if I already know the answer to this, but I want a sanity check (I'm working in 0V low, 5V high logic level):

In lieu of a multiplexer (because I had none), I have 32 transistors. The collectors are paired up and hooked to 16 inputs. The emitters are 32 discrete outputs. The bases are hooked up 16 each to the Q and Q' of a toggle.

The voltage of the base signals end up being 1V when "high," and when I would expect an output to be fully high, it is also about 1V.

I tried adding two extra transistors with the bases of each connected to Q and Q', and collectors tied to a small current limiting resistor at the voltage source. This helped a little, but only got me to about 2.5V and these two transistors got very, very hot.

Am I foolish, and this behavior from my hillbilly mux expected? Or should it work, and I likely have something wrong in my soldering?

EDIT: I forgot to mention, the transistors are 2N2222.

EDIT2: Added diagram of 4 resistors as example.

EDIT3: The outputs will be going into the data in / address inputs for a RAM chip, so they do not need to drive very much current. The Q and Q' are coming from a 74LS107 JK flip-flop with J and K tied together so that it acts as a toggle. As stated above, I tried using the Q and Q' signals to switch some other transistors tied almost directly (5V -> 150ohm -> collectors) to the power supply, but that caused them to overheat.

EDIT4: The RAM chips are two 6116P-3. Outputs O1a, O2a, etc are going to one chip, outputs O1b, O2b, etc are going to a second. This is done so that I have two buffers that the inputs can write to. The inputs which will target the I/O lines on the RAM come from a 74HC595 shift register. The inputs which target the address lines come from a CD4040 binary counter.