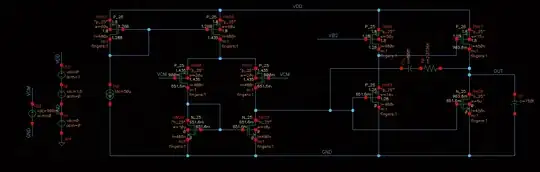

I designed the following circuit in Cadence Virtuoso:

It is a two stages op-amp with a compensation network (resistor and capacitor). VDD=1.8 V, VCM=900 mV, VB2=1.28 V. The DC gain is 73 dB.

1st question: I have to calculate the PSRR (power supply rejection ratio). The book on which I study defines the PSRR as the ratio between the differential gain and the gain from one supply (either VDD or GND) to the output. In order to find the gain from VDD to the output I placed a small signal voltage generator in series with VDD, as in the following picture:

With the two inputs set to the analog ground VCM=900 mV (I removed the input differential signal). I then made an AC analysis. Is this procedure correct to find the gain from VDD to the output?

2nd question: The AC analysis gives this result:

It seems to me that the small signal gain from VDD to the output is too much large: 30 dB. This means that if I have 10 mV ripple on the VDD line, then I will have more or less 300 mV at the output! Moreover, the PSRR = (73-30)dB = 43 dB. How can I decrease the gain from VDD to the output (thus improving the PSRR)?