The other answers missed the obvious, so here we go.

WM8804's SPDIF output uses LVCMOS 3.3V levels.

Then, you use TC7W04, a 74HC-equivalent chip powered from 5V. Its inputs are not really compatible with LVCMOS 3.3V, which is why it does not work.

Then we have a resistor divider which brings the output level down to +/- 0.5V.

To output +/- 0.5V levels, you don't need a chip powered from 5V. You can do it with a 3V3 chip just as well... and this 3V3 chip will be compatible with your WM8804 output. This removes all your problems.

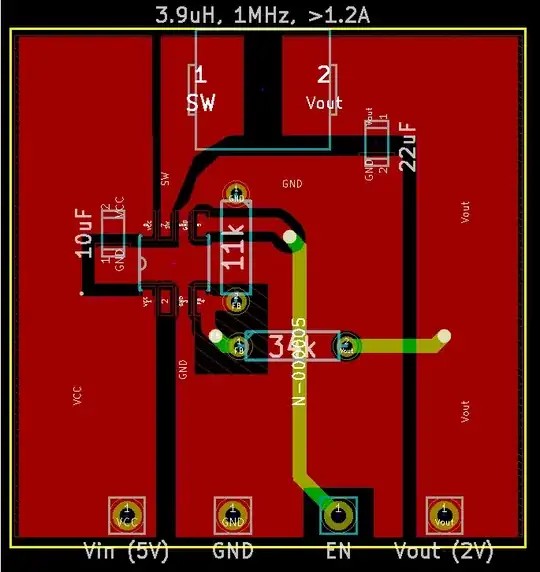

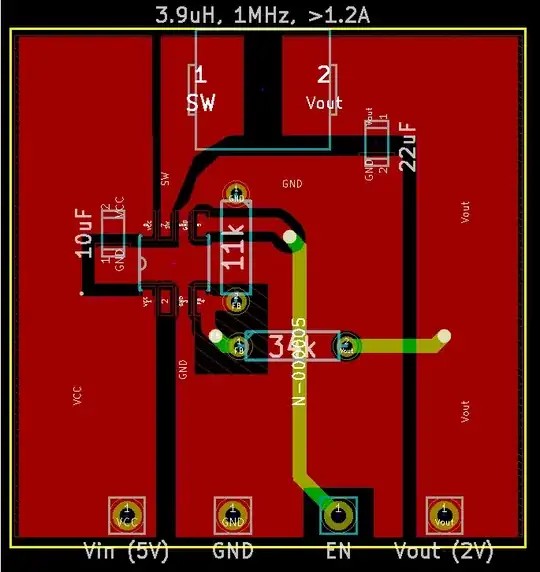

Solution #1 is straight from WM9904 datasheet:

WM8804 has a SPDIF output, and it is designed to drive a coax if you use the resistors specified in the application schematic which is provided... No need for extra complexity. Resistor values create a 75R source impedance and the correct voltage levels. This will work just fine with any chip that outputs 3V3 LVCMOS SPDIF.

If you want an exact 75R source impedance you'll need to adjust resistor values taking into account the exact output impedance of the chip. This is not likely to matter in practice.

Solution #2 ...

If you want to use a buffer, then it makes sense to use a chip powered from 3V3. Its input will be compatible with WM8804 output levels. You can use a 74LVC chip, for example. I wouldn't use 74HC powered from 3V3 as it will be a bit slow. Insert the buffer between the output of WM8804 and R8 in the above schematic.

You can probably use your existing board. Simply power your buffer chip from 3V3 instead of 5V (ie, cut the 5V trace and solder a wire to 3V3 instead) and change resistor values. The buffer should have adequate decoupling. If you're a perfectionist, add a ferrite bead in the supply line.

Note if the receiving DAC sucks at rejecting jitter, it will sound better with a higher value for C6, like 1µF.