Having a LDO output that is connected to digital circuitry, I would like to know the best way on how to place the bypass capacitors in this network. Is it better to place higher capacitance ones near the chip and low capacitance ones further away?

-

Which LDO would that be so we can look at the datasheet? Which types of capacitors and their values? In general, different LDOs want different properties from the output capacitors to work properly. – Justme Sep 16 '19 at 09:34

-

That depends on your load and cable or path inductance. If just nearby CMOS, it wont matter, but if a large surge current, then keep close to load. – Tony Stewart EE75 Sep 16 '19 at 18:59

-

Possible duplicate of [Decoupling with multiple caps per pin. Which should be closest?](https://electronics.stackexchange.com/questions/116927/decoupling-with-multiple-caps-per-pin-which-should-be-closest) – Rob Gilton Sep 24 '19 at 12:19

2 Answers

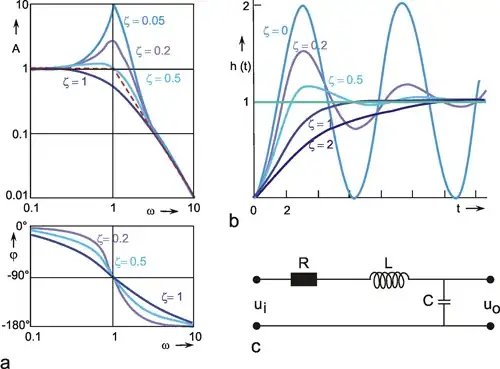

Considering capacitors having the same chip style, capacitors with higher capacitance have a lower resonance frequency, so the parasitic inductance will dominate at a (relative) lower frequency and therefore work worse for higher frequencies.

Source: "parasitic inductance of multilayer ceramic capacitors" from AVX

The parasitic inductance is dependent on chip size as is explained in referred document.

Increasing capacitance sometimes requires a bigger chip size (due to availability/pricing), so a bigger capacitance might increase inductance as well, but not necessarily (compare Table 3 in refered document).

In order to reduce EMI, current loop areas should be as small as possible, especially the high frequent current onces.

Therefore, generally, you should place the capacitor with the lowest capacitance closest to an IC and capacitors with higher capacitance further away.

UPDATE

The explanation regarding smaller current loop areas above applies for input capacitors (C1 and C2 below) as well as for output capacitors (C3, C4 and C5 below). When placing a higher valued capacitor (C4) closest to the output of a device (and leaving out C3) and a smaller valued capacitor (C5) further away, the smaller capacitor (C5) hardly contributes with respect to the output of that device.

Still there can be a smaller valued capacitor further away (shown as C6), but it is more likely that that capacitor serves as input capacitor for the electronics connected after it.

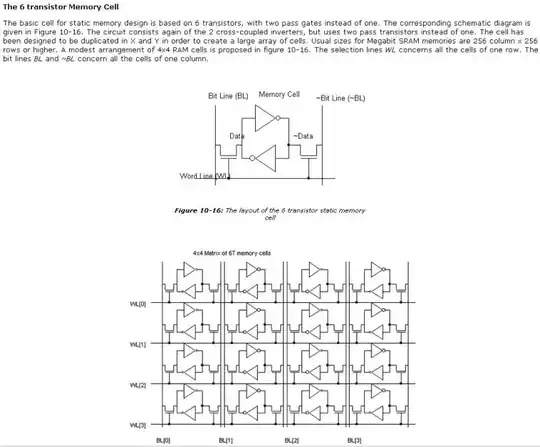

simulate this circuit – Schematic created using CircuitLab

In case of LDO's: a LDO may become unstable when placing too small valued capacitors at the output (due to low ESR). Moreover, a LDO is not a switching mode supply, so, there is no need to reduce high frequent current loop areas at its output. So, only a big capacitor at the output of the device will be sufficient.

- 10,594

- 2

- 19

- 40

-

examining the plot, I note the Impedance at 200MHz is about 1 ohm, for all three capacitors. Given 1nanoHenry at 1GigaHertz is +j6.3 ohms, I figure the inductance is about 0.8 nanoHenries [ 1 ohm = 6.3 * 200MHz * 1nH } for all three capacitors. – analogsystemsrf Sep 16 '19 at 12:18

-

1@analogsystemsrf I now see the point of your remark:capacitors with different capacitance, but with the same chip style have the same parasitic inductance. It can be easily seen because the capacitors share the same curve when the parasitic inductance is dominating ((right part of curves)) Other chip styles have different parasitic inductance (as shown in Table 3 of given link). I'll update my answer accordingly. – Huisman Sep 16 '19 at 13:01

-

This is a good explanation for all input bypass capacitors, but when you are connecting the output (not input) of and LDO to the rest of the circuit...would the higher capacitance ones be connected nearer to the LDO output or the smaller ones? – LazyTurtle Sep 20 '19 at 10:18

-

-

-

Hi @Huisman After checking several design guides I have realized that this placement issue can be addressed the other way round, please check the answer I have added. – LazyTurtle Sep 24 '19 at 10:44

Although @Huisman answer can be understood as a correct answer I´ve found, after checking multiple opinions and layout guides, that this topic can be addressed in multiple ways depending on how the circuit is understood.

The following site ("Step 3b: Output Capacitor Bank") reveals that the lower capacitance output bypass capacitors should be closer to the load, not the source, as it states:

"The smallest output capacitor, Co5, goes right near the output connector, or the load, if the load is on the same PCB, to clean up any high frequency noise before it disturbs the load. If high frequency noise gets into the output wiring harness, it will use them as an antennae to radiate. All the more reason to keep Vout nice and clean."

From this document and, taking into account all the previous theory on how capacitor work at high frequencies, a rule of thumb would be the following:

- For input bypass capacitors (supply input pins) place smaller capacitor closer to the IC.

- For output bypass capacitors (supply output, of LDO or DCDC converters i.e.) place smaller capacitors out from the IC, leaving higher capacitance capacitors closer to the source IC.

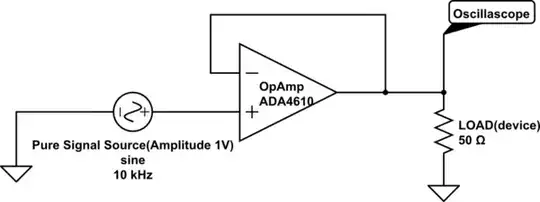

UPDATE Nonetheless, I´ve found several images of PCBs with this topology so that a good example would be the following image:

Please correct me if there´s something I´d be missing on this topic, but this seems to be a nice rule of thumb when proceeding to start the placement of the components in the PCB. Of course, depending on the circuit topology itself, this may need to be changed.

- 143

- 9

-

To quote my answer: [...] the smaller capacitor (C5) hardly contributes with **respect to the output of that device.** Still there can be a smaller valued capacitor further away (shown as C6), but it is more likely that **that capacitor serves as input capacitor** for the electronics connected after it. – Huisman Sep 24 '19 at 17:43

-

The article you refer to calls it **output** capacitor Co5. I would call that capacitor: **input** capacitor for the load as **it serves the load** to clean it from high frequent noise. – Huisman Sep 24 '19 at 17:48

-

I absolutely understand your position. But, nonetheless, taking a specific case in which you would have two different capacitors at the output, it may be better to place the smaller one out from the IC and the bigger one closer to it. Do you agree with this statement? – LazyTurtle Sep 25 '19 at 10:24

-

@uhuser6127833 No. When a device **generates** noise on its **input** (e.g.SMPS) the smallest cap should be placed closest to the IC's input to minimize high frequent current loop areas (HFCLA). When a device **generates** noise on its **output** (e.g.SMPS) the smallest cap should be placed closest to the IC's **output** to minimize HFCLA. – Huisman Sep 25 '19 at 11:44

-

If the **input** of the device needs to be clean, the smallest cap should be placed closest to the **input** IC in order to short high frequent noise. In the picture of your answer, C10 functions as **input** capacitor for connector with silkscreen label VOUT – Huisman Sep 25 '19 at 11:52

-

Putting a small cap on the output of the IC may lower the HFCLA, however, it may also cause instability. – Huisman Sep 25 '19 at 11:54

-

Wouldn´t, just for the reason you´re explaining, placing small capacitors closer to the load instead of the power source minimize the HFCLA? – LazyTurtle Sep 25 '19 at 13:16

-

**Which** HFCLA? The HFCLA of the power source or the HFCLA of the load? – Huisman Sep 25 '19 at 13:42

-

-

Yes, I would place a small capacitor closest to the load. But I would not called that an **output** capacitor, like the quote in your answer does. Because the capacitor serves the load, not the (output of the) IC. – Huisman Sep 26 '19 at 07:22