I believe I understand how memory reads work with the 8086 processor.

The 8086 has a 20-bit address bus and 16-bit data bus (multiplexed).

The memory module consists of two memory banks, and the LSB of the address bus is used to select which bank to access when reading a single byte. The remaining 19 bits provide the address within the memory bank.

When reading two bytes from a two-byte-aligned address, each memory bank contributes a single byte onto the 16-bit data bus.

As I understand, when reading two bytes from an unaligned address, the read is done in two clock cycles - first, the odd-address byte, and then the even-address byte, from the modified address (i.e. the original 19 bit address plus one).

My question is: why are two clock cycles required to accomplish this?

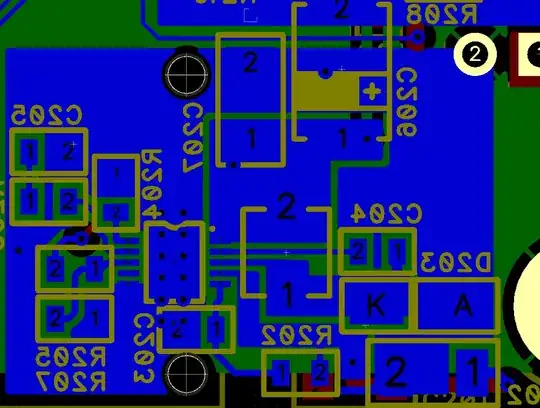

Can't it be done in a single clock cycle, using a simple adder and multiplexer, to put the two bytes in the correct order on the data bus?

Something like this: