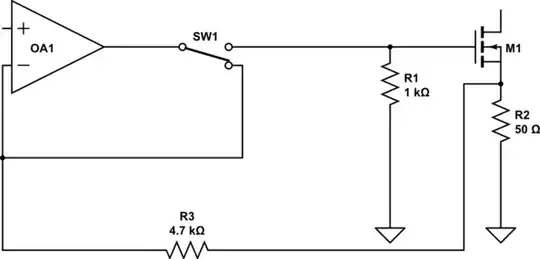

I'm using an ATMEGA3208 and I have configured the UART peripheral to open drain mode. I'm using an external pullup 1KΩ. I'm experiencing switching voltage spikes that goes negative. They are about 0.4V 500ns.

The spikes are only on receiver's side. The baud rate is 9600bps. The logic '1' is 3.3V.

I tried to increase the resistors to: R1 = R2 = 3KΩ. And R3 = R4 = R5 = R6 = 130Ω and the undershoot goes away. Of course that affects the logic '0' but it's still well below the threshold (0.3 x VCC).

They are exactly like this. However this answer doesn't help me as the mosfet is internal in the mcu. What can I do in this case?

EDIT: The undershoot is present even with 0.5m cables (multi copper standard wire 0.75mm)

Why does impedance matching matter in this case? Doesn't it matter only when the cables are much longer than signal's wavelength?

simulate this circuit – Schematic created using CircuitLab