Disclaimer: I'm designing a simple arduino based board, so I'm maybe over-complicating things, but I'd still like to do the board well.

I've carefully this answer : Decoupling caps, PCB layout, especially this part :

It doesn't take local planes to do this. I routinely use the local power and ground nets technique even on 2 layer boards. I manually connect all the ground pins and all the power pins, then the bypass caps, then the crystal circuit before routing anything else. These local nets can be a star or whatever right under the microcontroller and still allow other signals to be routed around them as required. However, once again, these local nets must have exactly one connection to the main board power and ground nets. If you have a board level ground plane, then there will be one via some place to connect the local ground net to the ground plane.

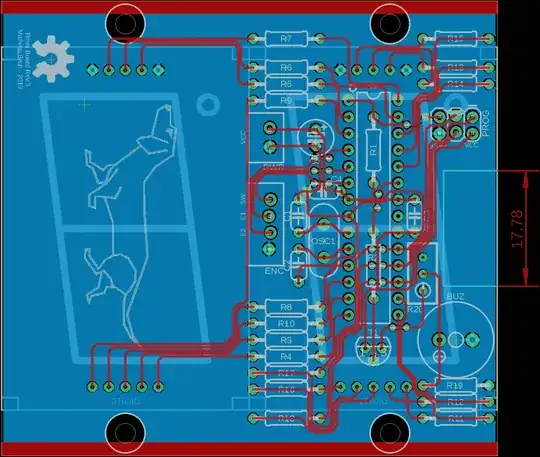

I now have this board:

Now, according to Aisler: https://aisler.net/help/design-rules-and-specifications/ultimate-guide-to-robust-pcb-design, I should add some pour on the top layer.

Should I use a dummy signal to accomplish this ?

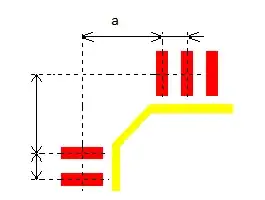

Edit : added detail on trace spacing :