Most but not all MOSFET have a low PTC which permits current sharing easily,. ALL CMOS logic has a PTC effect on Ron as well.

All BJT’s and IGBT have a NTC effect which requires a small series R (high power) to share current. It does this by the added resistance so that the NTC effect never causes thermal runaway with the rise in current with voltage yet drop in voltage with temp rise. So the net effect is to limit the current and share the current by linearizing this net resistance. This is usually just greater than the Rs of the diode, LED or Power transistor often defined as Rce.

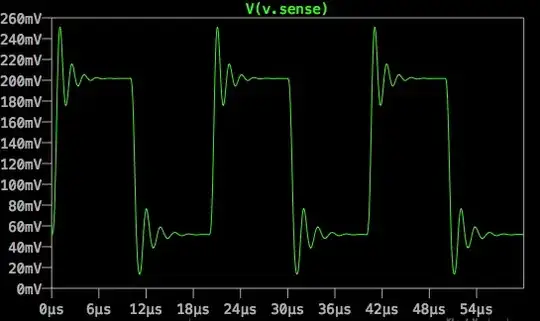

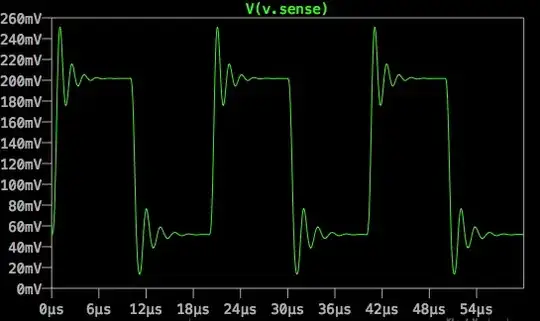

However MOSFETs in the Triode mode are not safe to current share as the heat is not evenly shared in nanolayers of HEXFET junctions on many parts designed as switches. In GW switches used on large power sources, this must be carefully done so that the linear changing Ron transition does not experience a commutation burst of power and be prone to failure and self heating. Deadtime is crucial based on L/R + RC time constants of the network load.

Is there a design you would like to share for heat reduction opportunities?

Sure you had thrown lower resistance at it in parallel FETS and if resonant expect higher Q, current amplification and resonant currents.

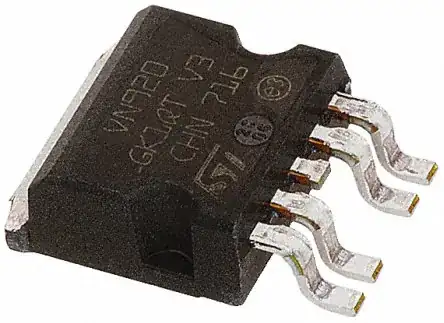

But instead, I would choose better FETs such as Silicon Carbide instead. SiC devices have 1% of the RdsOn (1mΩ/cm²) for same chip size, and 10x times higher breakdown voltage Vds max than the IGBT silicon devices for the same chip size. The drift region is also 10% of the Si FET which is \$W_{drift}≈ \dfrac{2V_{BR}}{E_C}\$ with this smaller region as 10µm vs 100µm.

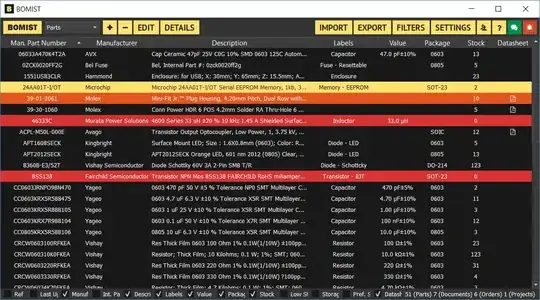

Here are some photo's of 10kW induction heaters.