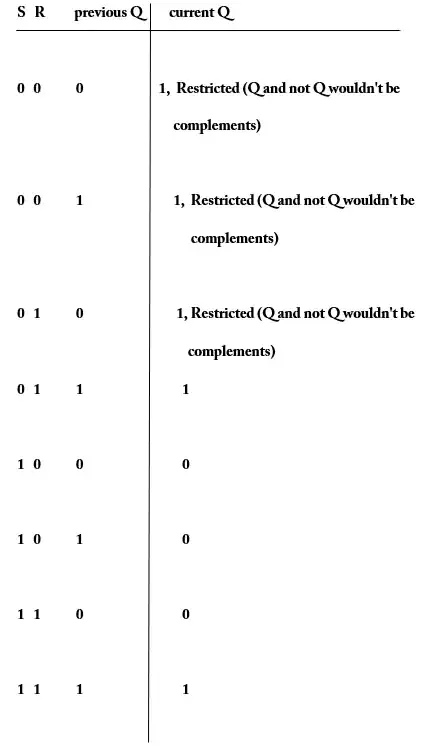

A precise definition of RS latch behavior should define it in terms of R, S, and previous Q and /Q values, recognizing that Q outputs and inputs may be stable high, stable low, or metastable. If either or both inputs is low, the states of Q and /Q will be ignored. If both inputs are high and Q and /Q are in any configuration other than high-low or low-high, both will go metastable, meaning their state cannot be reliably predicted unless or until one of the inputs goes low.

Many descriptions of RS latches, including responses to the "duplicate" question, would regard the "both inputs low" state as invalid, but setting the inputs to that state will not cause any kind of unpredictable behavior unless both inputs are switched simultaneously or nearly so (with the later one being switched before the Q and /Q inputs have stabilized to a high-low or low-high configuration).