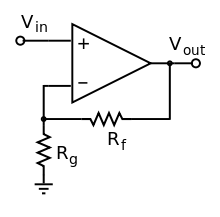

I've included a diagram of typical Pierce oscillator circuit taken from ST Application Note AN2867:

The note suggests that C_L1 and C_L2 should be chosen such that the following equation holds:

Since C_L1 and C_L2 are typically equal, this equation can be rewritten to solve for their value: C_Lx = 2(C_L-C_S).

As a rule of thumb, the stray capacitance is usually taken to be 2pF - 5pF, although I've seen a datasheet suggest 10pF as a rough estimate.

The question: By choosing an oscillator with a low load capacitance C_L, e.g. equal to the expected stray capacitance, C_Lx goes to zero. Is there any problem with choosing an oscillator with a small load capacitance and eliminating the need for the two capacitors C_L1 and C_L2 from a design by depending solely on the stray capacitance?