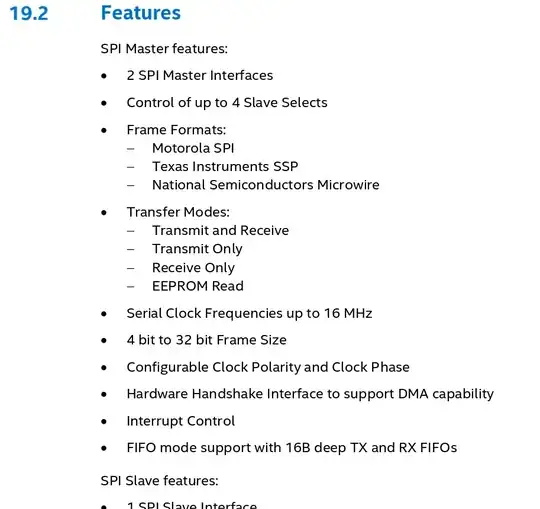

Im doing a design with a implementation of 1Gb ethernet switch, for that I bought a evaluation board to do it well.

The problem is that in the layout of the ev board I can check that the track impedance used to link the output of the chip (which has the PHY interface integrated) to the RJ45 connector is different than the right one which is suposed to be 100ohms as many routing guidelines for Ethernet say.

Here is the impedance calculation. (the values are taken from the layer stack and the design of the PCB that are included in the documentation associated with the user manual)

And here is the datasheet of the evaluation board that Im using:

http://ww1.microchip.com/downloads/en/devicedoc/50002587a.pdf

Any idea why the differential impedance (83,73ohm) is so far from the ideal 100ohms recommended in ethernet routing?

thank you all!