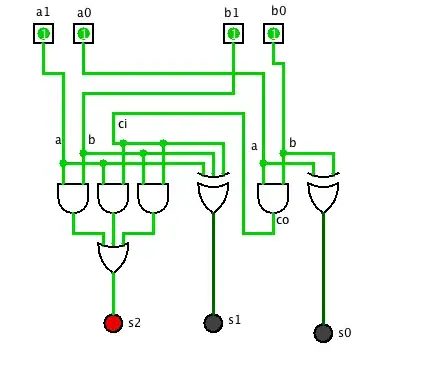

I attempted to build an 8-bit adder in Logisim by carefully chaining together a half-adder and 7 full adders, all made from basic logic gates. Unfortunately, it produced erroneous results; for example, 00000011 + 00000011 = 000000100 ! I found that the problem seems to occur around the half-adder and the least significant bit, so I tried to pinpoint it with a smaller, 2-bit adder:

As you can see (unless I am going crazy), this one is off, too; s1 should also be lit! I can see why it's not lit; a0 and b0 produce a carry bit, which, along with a1 and b1 (or even if it DIDN'T carry), makes the XOR gate for s1 false. But from the book I am using, this should be the way to hook them up? What am I missing here?