Here is what I expected to happen:

A B C D

0 0 0 0

1 0 0 0

1 1 0 0

1 1 1 0

1 1 1 1

0 0 0 0

...

Initially, suppose all flip flops have output 0. Then, Q' of the last flip flop is 1, so all flip flops are in a stable configuration. On the next clock pulse, first flip one flips to 1 (because of Q' of last flip flop), and so on.

After the 3rd pulse of the clock, the flip flops are in the state 1 1 1 0.

On the next pulse, here's what I think should happen: Last flip flop takes in a 1, forcing it's Q' to become zero. That resets all the previous flip flops to 0. After resetting to 0, the output of first flip flop resets the last flip flop, effectively cycling back to the initial state with all flip flops being 0.

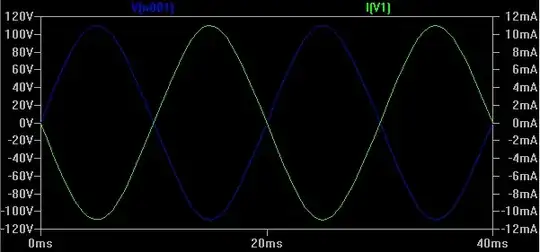

I reckon I have made some mistake in reasoning over here because it appears to not behave like that when I simulated it with QUCS. (I didn't have access to digital simulation in it but worked with transient simulation, so I might be wrong here too)

Any input is very much appreciated.