Here are a few clues to get you going.

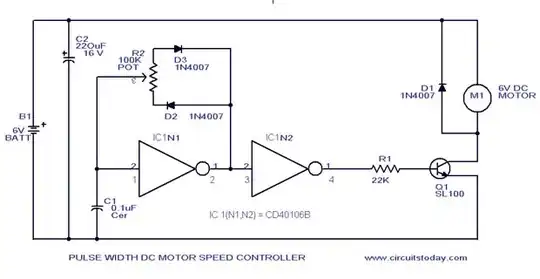

simulate this circuit – Schematic created using CircuitLab

Figure 1. OP's schematic with U1 inputs labelled. It's not shown here but the circuit needs a split-rail power supply to work. e.g., +/-12 V.

Consider that the circuit has just been powered up. If everything was ideal then the op-amp inputs and outputs would be at 0 V and nothing would happen. Fortunately for this circuit real op-amps aren't ideal and have slight differences in the input offset voltages and this is enough to kick the circuit into life.

I've shown U1's non-inverting input at +1 mV and the inverting input, n0, at 0 V.

- In that condition what will happen at n1?

- What that initial change happens at n1 what will the voltage be at U1's non-inverting input?

- Meanwhile what's happening to the voltage at n2? (Caution: trick question.)

- What's happening at n3?

Sketch that part out and post a photo into your question and we'll go from there.

From the comments:

Well, when the input reaches high enough level we will have logic zero at the output of the Schmitt trigger.

This suggests some slightly mixed up thinking.

- This isn't a logic circuit - it's analog so while U1 can switch high or low they're not really 'logic' levels.

- You are correct if you mean that the output switches low but what is low in this circuit? (I gave you a hint in the caption of Figure 1.)

Also, I think that same thing should happen in n2 since those points are separated only by a single resistor.

No, n2 is what's known as a 'virtual ground' due to the negative feedback caused by C1. R3 controls the current into the integrating capacitor. If the op-amp output is not in saturation then the output will adjust to maintain n3 at (or very, very close to) the voltage on the non-inverting input, 0 V. See How does an op amp integrator work? where this is currently under discussion.