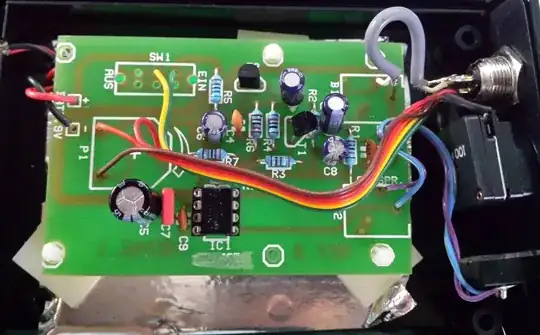

Currently, this is the only assembled part on the circuit board. This is a simple inverting buffer circuit that should be at the input. The op-amp (LTC6241HV) is powered +/-5V from a linear bench power supply. The power pins are bypassed with 0.1uF caps.

I'm inputting a 1KHz sine and on the output I get a ~405KHz sine superimposed on the 1KHz signal. I have tried to build a second PCB but the results are exactly the same.

If anyone knows what could be the cause for this I'll be happy to hear.