I found this from wikipedia page. It says, data is sampled after SCL line rises.

- 397

- 3

- 8

-

2And what exactly is your question? – olltsu Dec 09 '18 at 07:32

-

1@olltsu NXP I2C document only says that **The data on the SDA line must be stable during the HIGH period of the clock.** So I had a doubt that do I have to provide a small delay before applying clock for the data line to settle. `SDA=1; SDA=0; SCL=0; SCL=1;` – Lelouch Yagami Dec 10 '18 at 09:16

-

Yes, you do, see my answer below for more details on how long or short this must be. – Joseph Glover May 29 '20 at 00:05

2 Answers

To be a bit more precise, the data isn't just sampled at the rising edge, but must change before the rising edge and be stable for the entire HIGH period of the SCL.

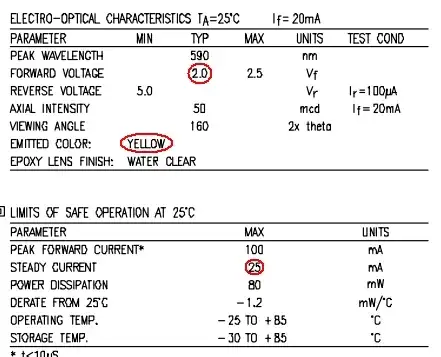

This screenshot was taken directly from the I2C Specification.

Note: The ACK bit must follow this as well:

More about timing

After reading your comments on your question you seem to be curious about whether there should be a delay after you change your SDA before you change your SCL. The answer is yes, but it's all dependent on what mode your device will operate in. See tables 9 and 10 of the specification. Table 10 specifically refers to the timings, which may be what you're interested in.

For some very basic numbers, here are the min and max for Standard-mode for data setup and hold (min in left, max in right):

If you notice, the data hold time has 0, but there is a caveat:

This is simply restating what you see on the last row of the above picture, the maximum fall time of the SCL or SDA lines in Standard-mode must be under 300 ns, therefore the data hold time should be at least 300 ns to account for the slowest possible SCL transition.

In Standard-mode, VIHmin (the minimum input voltage to be considered high) is 0.7V. VILmax (the maximum input voltage to be considered low) is 0.3V. That means the range between 0.3V and 0.7V is unstable.

What all this means

Assuming you are operating in Standard-mode:

- SDA must be setup (moved to a stable range) 250ns before SCL goes high.

- SDA must be stable for the entire HIGH period of SCL.

- SDA must be held for 300ns while SCL goes low.

Saying "while" here seems a bit strange, but it's to emphasize the 0 + 300ns minimum needed for SCL transition back to low. Typically I believe the hold time will be (1/2*SCLperiod) + 300ns. More information can be found in Table 10 of the specification to understand what operating mode you are dealing with.

- 216

- 2

- 5

I2C data line (SDA) is sampled at the rising edge of I2C clock line (SCL).

It is not sampled after the rising SCL, it is sampled with rising SCL.

- 6,471

- 1

- 11

- 22

-

Timing is never perfect. It could be sampled a fraction of a nanosecond before or after the rising edge of SCL. – The Photon Dec 09 '18 at 15:36

-

4@ThePhoton ?? It couldn't be sampled *before* the rising edge, as there is no clock then by definition. The rising edge triggers the sampling, hence the SDA line must be stable when the clock rises. – awjlogan Dec 10 '18 at 10:49

-

1@awjlogan, it can if there's more delay in SDL than SCL between where you measure them and where the chip actually samples them. – The Photon Dec 10 '18 at 15:38

-

@ThePhoton That would just lead to metastability, there's no way it would be designed to allow that scenario. It's the whole reason to have setup and hold specifications. https://www.edn.com/design/analog/4371393/Understanding-the-basics-of-setup-and-hold-time – awjlogan Dec 10 '18 at 20:58

-

1Yes, it's the whole reason you need setup and hold specs. But it's possible for the minimum hold time to be negative (due to built in delay in the data input). This is very common in FPGAs, for example. An I2C device won't have a negative minimum hold time, but depending how you measure it, it might actually have a negative sampling time. – The Photon Dec 10 '18 at 21:00

-

...by, like I said, maybe a fraction of a nanosecond. Which will be totally insignificant in a reasonable I2C design. – The Photon Dec 10 '18 at 21:07

-

So, yes, I was being a bit pedantic. I wasn't expecting that comment to blow up into a bunch of replies. – The Photon Dec 10 '18 at 21:13

-

1@ThePhoton Well, I learnt something (negative setup times), no blow up intended :) – awjlogan Dec 11 '18 at 09:50