I am designing some boards that are powered and communicate through Cat 5 cables using a bit banged form of protocol inspired by quad spi.

Using the bus network topology in a half duplex manner, I am able to communicate reliably with 10kHz clock.

Since I am using the classic atmega328p-au do I have to worry about putting an external clock or it should do the job fine with just the internal RC circuit?

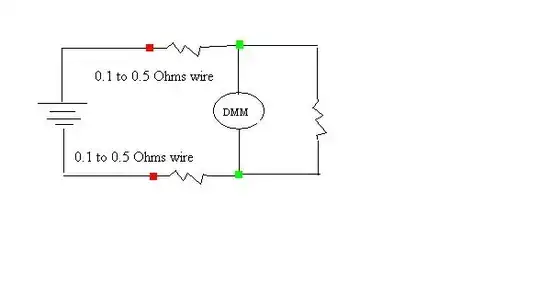

Modified image of this: