What is the best practice for routing high current traces through the pads of small 0603 components?

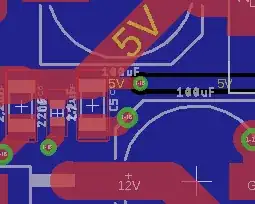

I have a wide high current trace which that passes through a 0603 decoupling capacitor.

Initially I kept the thickness high(like below) but someone suggested that due to lack of thermal reliefs this would make the component difficult to solder or prone to tombstoning.

Do I instead take a thick trace as close to the pad as possible and then jump with a thinner trace like below?

What impact would this have on the current carrying capabilities? What is the best practice in this case?

This is a 2 layer board.