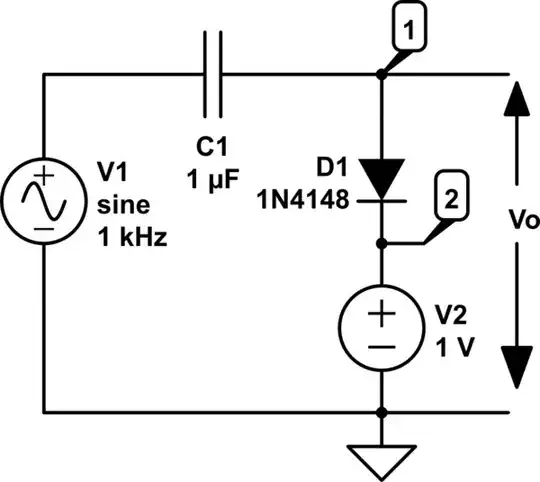

Shown below is the circuit I would like to implement. (the circuit is from this paper).

Basically, it's a circuit designed to cut off voltage when electrochemical etching is done. The sudden drop in current flow is taken as the signal to stop the voltage bias.

I circled the two parts I would like to better understand.

Given the schematic of the circuit, I would like to know the voltage difference between 'WIRE' and 'RING' (circled in blue), assuming the state where Q1 and Q2 have zero Gate voltage and hence all the current is just flowing down to WIRE and RING.

There is a switch (circled in red) connected to CLR pin of the flip-flop. I looked at the datasheet of DM7474 flip-flop. I initially thought it was some manual switch that maintained the voltage between 'WIRE' and 'RING' but given the output of Q's dependence on CLR input, it doesn't seem so obvious. Neither high nor low of CLR fixes the output of Q.

-----added-------

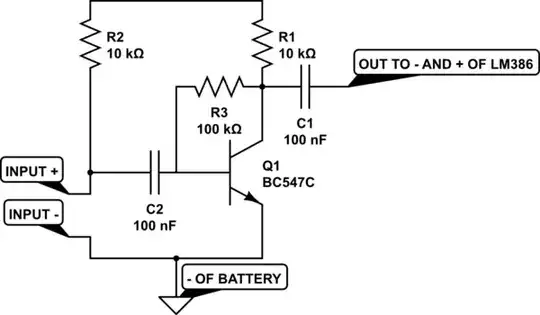

Thank you for your suggestion. After your explanation, I wrote down what voltage value the gate of Q3 would get as a function of resistance values of 'WIRE/RING' and potentiometer.

Since no current goes into Q3 gate, I \$= \frac{8V}{R_2 + x_w + x_p} \$.

So I guess I have to choose my potentiometer value such that the gate voltage of Q3 gets some voltage above the threshold when in the process of etching and gets zero when the etching is over (since when etching is done, the resistance value will shoot up).

-----added-------

I circled the potentiometer, capacitor, and another switch. I think I understand why the potentiometer is there. It is to introduce a potential value change to the input of the flip-flop.

I am not sure what role the capacitor and switch in parallel with the potentiometer serves.