I am using an SiT1552 MEMS TCXO providing 32.768 kHz. It will be sourcing two ICs: a microcontroller and a DA14580 Bluetooth Low Energy transceiver.

The ICs and TCXO are all powered by 3.3V. The TCXO output is the standard 10%-90% LVCMOS voltage swing. It can drive up to 100 pF. It is not AC-coupled.

The MCU is happy with this voltage swing. It wants ~50% duty cycle.

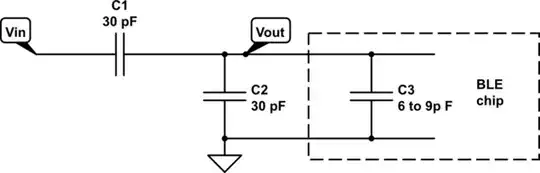

The BLE clock input, however, is internally AC-coupled and needs a 0.1 - 1.5V (pk-pk) voltage swing.

In an app note which requires registration to view, it suggests to use a series capacitor for attenuation:

I can do this with a larger cap so as to attenuate the signal even more. The TCXO can handle the extra load.

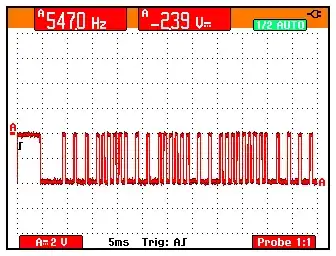

Here is the result.

- Does it look sane?

- Will the MCU remain happy?

- Is there a better method?

.

simulate this circuit – Schematic created using CircuitLab