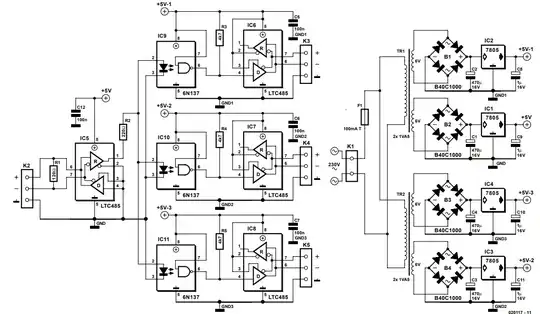

The circuit seems to be an Elektor RS485 splitter with three optically coupled outputs and independent 5 V supplies. The circuit is uni-directional as is obvious from the orientation of the opto-couplers IC9, 10 and 11 and data flow is from left to right.

The LTC485 is a low power RS485 Interface Transceiver and, since it has only two wire connection it must be half-duplex so the receiver, R, and driver, D, buffers can't be enabled simultaneously. In this uni-directional application they can be left on.

Page 5 of the LTC485 datasheet states:

\$ \overline {RE} \$ (Pin 2): Receiver Output Enable. A low enables the

receiver output, RO. A high input forces the receiver output

into a high impedance state.

\$ {DE} \$ (Pin 3): Driver Output Enable. A high on DE enables

the driver outputs, A and B, and the chip will function as

a line driver. A low input will force the driver outputs into

a high impedance state and the chip will function as a

line receiver.

So IC5 is using the 'R' buffer and needs pin 2 low and pin 3 high. The others are using the 'D' buffer and require the opposite.

What I see normally for a 100 nF capacitor, is that it is located between pin 5 (GND) and pin 8 (VCC), but other pins needing 5V are directly going to VCC (not through the 100 nF capacitor).

The 100 nF capacitor is there to provide very short term energy supply during spikes in current demand by the IC it is connected to. If it were not there the inductance and resistance of the PCB traces would result in dips in voltage which would make the device's operation unstable or unreliable. Nothing is connected to ground through the capacitor. The idea is that the +5V rail is definitely +5 V.

I tried +5V, but doesn't work, not sure if it is for this reason, but the IC got warm, found out too late and before that replaced by others which probably are ruined too.

Check and recheck your wiring.

From the comments:

You say pin 2 and 3 should be low resp high. But if you look in the circuit than IC6, pin 2 and 3 are connected together, so how they can be different?

(There was an error in my answer. DE should not have a bar over it. Fixed.)

Figure 1. Notice the logic inversion symbol 'o' at (1) and that it's missing at (2).

The clever chaps who designed the chip realise that since you will be transmitting or receiving that you are likely to want to switch the two lines simultaneously. By inverting the logic on pin 2 they save you having to add an external inverter. You can now wire the two together.

- Pin 2 + 3 high: D enabled. R disabled (high impedance).

- Pin 2 + 3 low: D disabled (high impedance). R enabled.

Be aware that the R and D buffers are tri-state. The outputs, when enabled, can be high or low and when disabled are high-impedance and, effectively, disconnected.