I have designed a product for a customer, that now needs to pass UL/FCC/CE Testing, It passed UL & FCC but failed CE for both 8kv ESD and EMI. The Chinese test lab my client went through sent me back a markup of what they "did" and suggest. The images of the physical board do not match the schematic recommendation, and the schematic seems odd to me.

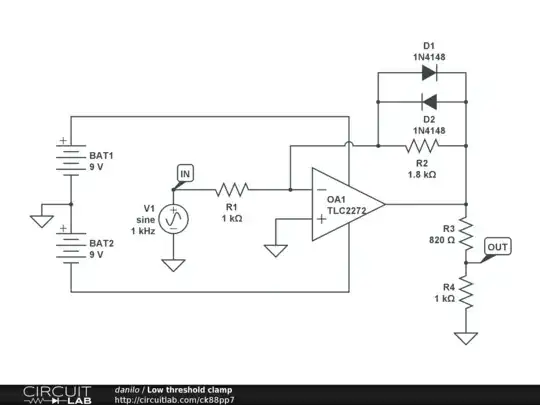

I was expecting more of a "low pass" filter design to stop ESD and EMI from entering my device via a micro USB port, and an LED close to the package edge (ESD only).

Below is what I was going to do, and what they propose on the schematic. Can anyone give any insight as to they they have Ferrite beads past any capacitors, and have two, one for a 1mA LED and the other for a up to 370mA LiPo charger?

Circuit And Failure Info:

My highest clock is in the micro controller at 1MHz, and I drive a 100mA fan with a 16kHz PWM... I failed EMI for signals in the 100's of MHz, that are not integer multiples of 1MHz. So I'm fairly sure it is from the 3rd party USB charger that is charging my product.