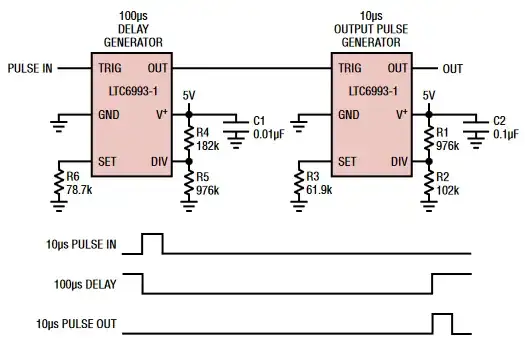

I need to design a circuit to delay an input signal by a given amount of time (around a second, trimmable). The delay should be set through the use of passive components (resistors or capacitors). The input signal is basically a TTL level that goes high at a certain time, stays high for some time (100ms should be nice value), then goes back low.

I cannot use a micro or other programmable device because the firmware certification process is too expensive.

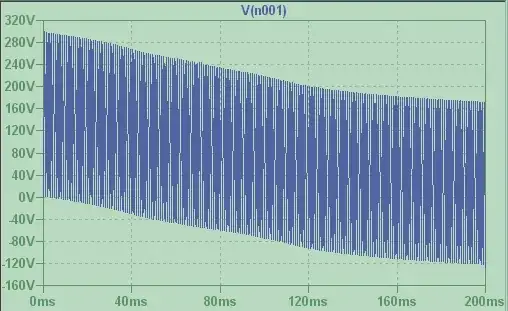

I realized a working solution that uses an RC network feed into a Schmidt triggered comparator (with a fixed voltage reference placed in input against RC voltage level). I'm not very satisfied with this solution for two main reasons:

- the needed delay implies large caps that are pretty inaccurate;

- the input signal high level need to last at least as much as 'delay';

Overall requirements:

- delay duration 1 sec +/- 500 ms accuray +/- 10%

- The delayed event should last for a reasonable time lets's say at least 100ms (and less than 200ms).