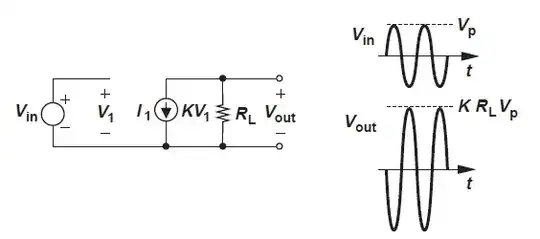

Do you know what (VCCS) voltage controlled current source is?

And that a MOSFET transistor can be treated as a VCCS?

And because the MOSFET gate current is /$0A/$ the \$V_1\$ source is left open (MOSFET input resistance is equal to infinity).

Also, notice the direction of a current source. This current source is pointing downwards. And this is the key here.

For a positive \$V_1\$ voltage the current at the output will flow in the direction shown by the arrow in the current source symbol.

And this current will result the negative voltage across \$R_L\$ resistor.

Do you know why?

But for the negative \$V_1\$ voltage the \$ K\cdot V_1\$ current will flow in the opposite direction. And this will give you a positive output voltage across \$R_L\$ resistor.

See the example for \$K = 0.1S\$ and \$R_L = 100\Omega\$

And what is important to notice is that for a positive input voltage we have a negative output voltage and the opposite is true for negative input voltage (output voltage is positive). And this is why you have a minus sign in the equation. In reality, this minus sign only informs us that our amplifier output voltage is 180° out of phase with respect to the input voltage.