I'm looking at the following datasheet for an accurate TCXO: TG2016SBN

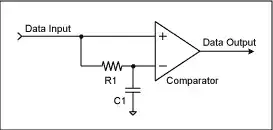

It gives values for Rload and Cload, and AC coupling cap - which I've incorporated into a clock pulsing circuit. Will a simple comparator (with a bit of hysteris) be enough to clean this signal up for a CMOS clock input?

I've currently got the following circuit sketched up. The 20Ks should will give a paralel (small signal) load of 10K, and bias it at 1.65V DC coupled. I don't see anything wrong with it - the comparator is fast enough and in theory work.

The comparator is the following: LT6752

Cheers